## Front-end electronics for high counting rate TRD

A. Caragheorgheopol<sup>1</sup>, D. Bartoş<sup>1</sup>, V. Catanescu<sup>1</sup>, V. Văleanu<sup>2</sup>, and V. Vasiliu<sup>2</sup>

<sup>1</sup>NIPNE, Bucharest, Romania; <sup>2</sup>ISS, Bucharest, Romania

Fast Analog Signal Processor FASP-0.1 [1, 2] is a prototype ASIC designed at NIPNE for HCR-TRD having in mind the CBM experiment at FAIR. In this contribution we report on relevant measured parameters of ASIC analog channels and a FEE based on FASP, designed and built for in-beam tests of our HCR-TRD prototypes [3].

The measured ASIC parameters [4, 5] are:

- quiescent supply current (V<sub>D</sub> = 3.3V): 30mA  $\pm 1$ mA. - output baseline shift :

- with power supply (V<sub>D</sub> = 3.0-3.6V): < 0.07%;

- with detector leakage current (I<sub>L</sub>= $\pm$  50nA): <9 $\mu$ V/nA.

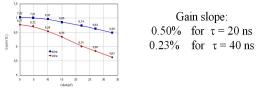

- conversion gain G vs. C<sub>det</sub> (for FAST outputs):

Figure 1: Conversion gain G vs. Cdet

- integral nonliniarity (INL)(0-1V linear range): INL = 1.0% for  $\tau$  =20ns, FLAT output; INL = 0.2% for  $\tau$  =40ns, FAST output.

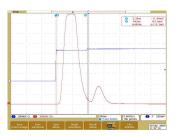

- overload recovery (for FAST outputs,  $\tau = 40$  ns): first pulse: x10 overload ; second pulse: after 400ns (corresponding average pulse rate > 300kcps).

Figure 2: Overload recovery

- electronic noise charge ENC vs.  $C_{\mathit{det}}$  for FAST outputs:

Figure 3: ENC vs. C<sub>det</sub>

Front End Electronics (FEE) was designed to cope with the requirements for in-beam test of 3 different HCR-TRD prototypes. The requirements are:

- acceptable immunity to the "pick-up" noise;

- long transmission line of detector signals to ADC;

- NIM logic standard for request/grant protocol;

- 16 analog signal channels for each detector (48 total).

FEE is splitted in two units (Fig.4). The first one, motherboard, houses one FASP ASIC for wich it provides power supply, all DC references voltages (THRESHOLD, BASE-LINE,etc.), 8 analog buffers with differential outputs (each buffer can be switched to handle FAST or FLAT TOP signal), and NIM logic standard interface (EVT, REQ, RDY, RST signals). Motherboard is a three layers PCB of 100x120mm<sup>2</sup> size. The second one, adapter board, has two identic sections. Each section has 8 differential input channels providing single-ended outputs. DC output levels can be adjusted to match ADC inputs. Adapter board is three layers PCB of 78x74mm<sup>2</sup> size.

Figure 4: ASIC MB (Left) and Adapter(Right)

Figure 5: Experimental set-up used in the in-beam test

HCR-TRD prototypes, the described FEE (48 channels) and geometry control mechanism (Fig.5) were succesfully tested at T10 beam line of the CERN PS accelerator, last November .

## References

- V.Catanescu, CBM 10th Colaboration Meeting, Sept. 25-28,2007, Dresden

- [2] V.Catanescu, et al., DPG,Bochum, March 18,2009

- [3] M.Petris et al., contribution to this Sci.Rep.

- [4] A. Caragheorgheopol et al., 14th CBM Colaboration Meeting, Split,Oct.6-9,2009.

- [5] A. Caragheorgheopol et al., CBM FEE/DAQ Workshop, Feb. 22-23,2010,GSI