# The n-XYTER Reference Manual

— chip version 1.0 —

A.S. Brogna<sup>1</sup>, S. Buzzetti<sup>2</sup>, C.J. Schmidt<sup>3</sup>, H.K. Soltveit<sup>4</sup>, U. Trunk<sup>5</sup>,

W. Dabrowski<sup>6</sup>, T. Fiutowski<sup>6</sup>, R. Szczygiel<sup>7</sup>, P. Wiacek<sup>6</sup>

— ASIC Laboratory, Kirchhoff-Institut für Physik, Heidelberg, Germany —

— Detector Laboratory, Gesellschaft für Schwerionenforschung mbH, Darmstadt, Germany —

— The DETNI collaboration —

Editor: C.J. Schmidt

document version: 1.30 (DRAFT) July 24, 2008

#### Abstract

HUHNHUHN This paper describes in detail electrical specifications, operating conditions and port definitions of the readout chip  $n\text{-}XYTER\ 1.0.$  The ASIC development as a part of the EU-FP6 project DETNI within NMI3, is designed to be connected to three different, solid converter based neutron counting area detectors. They are to supplement future high intensity research applications at modern neutron sources. Each of these detectors is specified to house between  $10^5$  and  $5\cdot 10^5$  pixels in a single module with an overall neutron detection rate of up to  $100 \mathrm{MHz}.$

Because of the the statistical, non-triggerable nature of neutron data to be processed, the internal architecture of the chip is self triggered and data driven. It integrates 128 channels with low noise preamplifiers and shapers. Each channel has two different shapers with distinct time constants, one optimized for timing resolution, the other one optimized for energy (pulse height) resolution. A peak detector connected to the slower shaper allows for the application of a spectroscopic amplitude measurement.

An internal time stamp generator provides the temporal reference that may be employed to identify time coincidences of signals on different detector channels and thus correlate their spatial point of origin.

For testability and calibration purposes, a charge injector with adjustable pulse height was implemented. The bias settings and various other parameters can be controlled via a standard  $I^2C$ -interface.

<sup>\*</sup>Email: C.J.Schmidt@GSI.de

# Contents

| 1            |      | p Architecture                                                          | 8          |

|--------------|------|-------------------------------------------------------------------------|------------|

|              | 1.1  | Front End                                                               | 8          |

| 2            | Elec | ctrical Specifications                                                  | 15         |

|              | 2.1  | DC Characteristics                                                      | 15         |

|              | 2.2  | Power Dissipation                                                       | 15         |

| 3            | Оре  | erating n-XYTER                                                         | 17         |

|              | 3.1  | Front-end Pulse Shape                                                   | 17         |

| 4            | Con  | figuration and Control of the $n$ - $XYTER$ , Slow Control              | 18         |

|              | 4.1  | I <sup>2</sup> C Interface                                              | 18         |

|              |      | 4.1.1 Mask Registers                                                    | 19         |

|              |      | 4.1.2 Bias Registers                                                    | 20         |

|              |      | 4.1.3 Configuration Registers 32 and 33                                 | 23         |

|              |      | 4.1.4 Overflow Counter, Registers 34 - 35                               | 23         |

|              |      | 4.1.5 Missing Token Counter, Registers 36 - 37                          | 23         |

|              |      | 4.1.6 Trim DAC Shift Register 42: Local Threshold and Indi-             |            |

|              |      | vidual Channel Shut-Down                                                | 24         |

|              |      | 4.1.7 Delay Registers                                                   | 25         |

|              | 4.2  | Signal Polarity Configuration                                           | 26         |

|              | 4.3  | Test Channel                                                            | 27         |

|              | 4.4  | Channel Shutdown                                                        | 27         |

|              | 4.5  | Reset Modes                                                             | 27         |

|              | 4.6  | Test Modes                                                              | 28         |

|              | 4.7  | Internal Test Pulses                                                    | 29         |

|              | 4.8  | Comparator Operation and Time Walk Compensation                         | 30         |

|              | 4.9  | Clock Signals                                                           | 32         |

|              |      | 4.9.1 Time Stamp Generation                                             | 33         |

|              |      | 4.9.2 Readout clocks                                                    | 35         |

| 5            | Dat  | a Transfer                                                              | 35         |

|              | 5.1  | Digital Output Format and Timing                                        | 36         |

|              | 5.2  | Analogue Data Transfer, Timing                                          | 37         |

| 6            | Kno  | own Problems and Limitations                                            | <b>4</b> 4 |

|              | 6.1  | Cadence database information                                            | 44         |

|              | 6.2  | Things to be included/ done in the next version of $\textit{n-XYTER}$ . | 44         |

| $\mathbf{A}$ | Fro  | ntend Schematics                                                        | 45         |

| В            | I/O  | Pads Description                                                        | 70         |

|              | ,    | Front Pads                                                              | 71         |

|              | B.2  | Bottom Pads                                                             | 86         |

|              | В.3  | Backside Pads                                                           | 92         |

|              |      | Top Pads                                                                | 96         |

| $\mathbf{C}$ | Inn  | ut Impedance Simulations                                                | 101        |

| D       | Test Board                           | 106 |

|---------|--------------------------------------|-----|

| ${f E}$ | Gray code tables for the output data | 118 |

# List of Figures

| 1  | <i>n-XYTER</i> chip architecture                                             | 8     |

|----|------------------------------------------------------------------------------|-------|

| 2  | Schematic of the front-end, including FAST and SLOW shaper                   |       |

|    | branches                                                                     | 9     |

| 3  | Transient response of the pre-amp                                            | 11    |

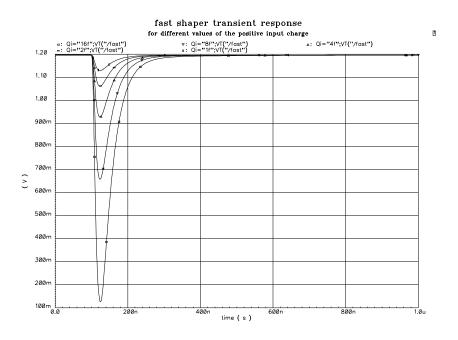

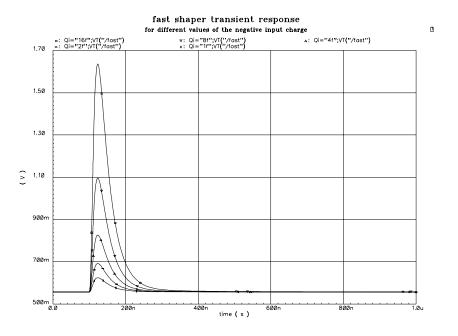

| 4  | Transient response of pre-amp and fast shaper                                | 12    |

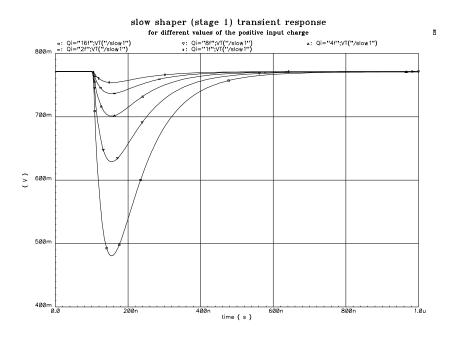

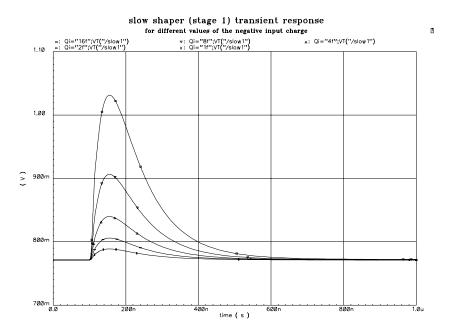

| 5  | Transient response of pre-amp and slow shaper $(1^{st} \text{ stage})$       | 13    |

| 6  | Transient response of pre-amp and slow shaper chain                          | 14    |

| 7  | Semi-Gaussian pulse with the corresponding parameters                        | 17    |

| 8  | I <sup>2</sup> C-bus write and read sequences for accessing registers on the |       |

|    | n- $XYTER$                                                                   | 19    |

| 9  | mono-stable and iDur                                                         | 22    |

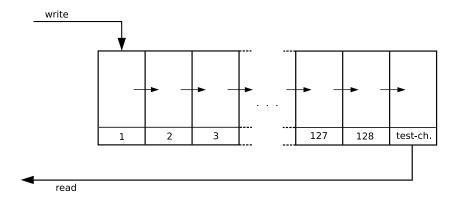

| 10 | shiftregister principle                                                      | 24    |

| 11 | Simplified schematic of the delay buffer                                     | 25    |

| 12 | Generation of test signals                                                   | 29    |

| 13 | Block diagram of the connection between calibration circuit and              |       |

|    | channels inputs                                                              | 31    |

| 14 | Injected positive charge during the calibration procedure                    | 32    |

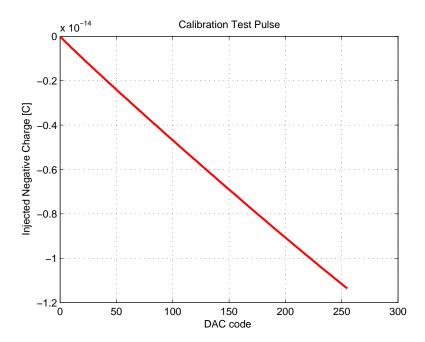

| 15 | Injected negative charge during the calibration procedure                    | 33    |

| 16 | Time-stamp generation principle                                              | 34    |

| 17 | Output data diagram                                                          | 37    |

| 18 | Suggested circuit to convert the time-stamp from Gray-code to                |       |

| _  | binary-code                                                                  | 42    |

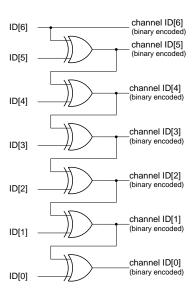

| 19 | Suggested circuit to convert the channel ID from Gray-code to                |       |

|    | binary-code                                                                  | 43    |

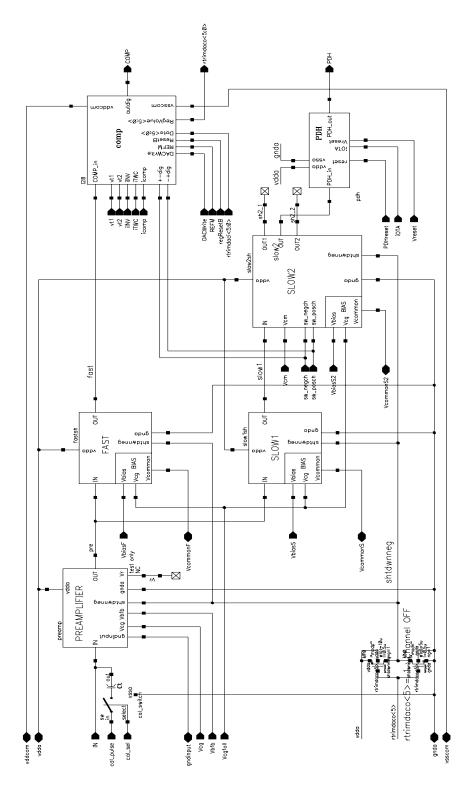

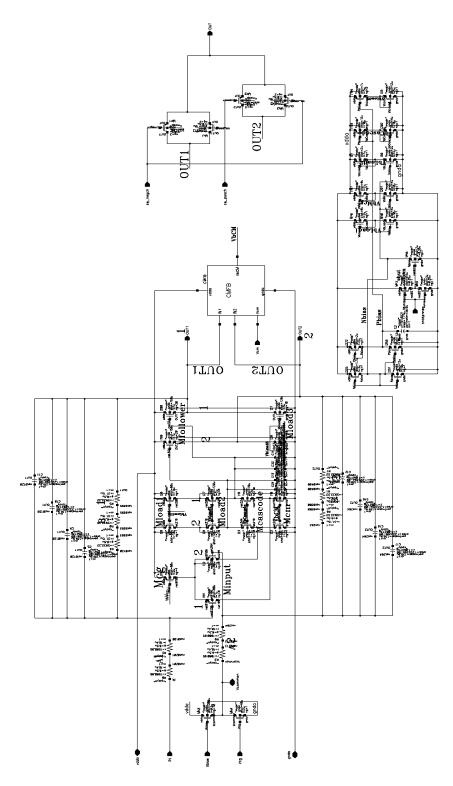

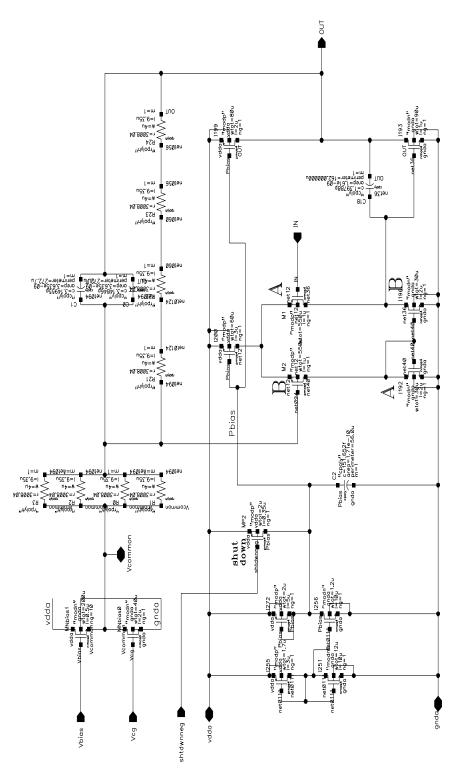

| 20 | n- $XYTER$ front-end schematic; cellname: frontend                           | 46    |

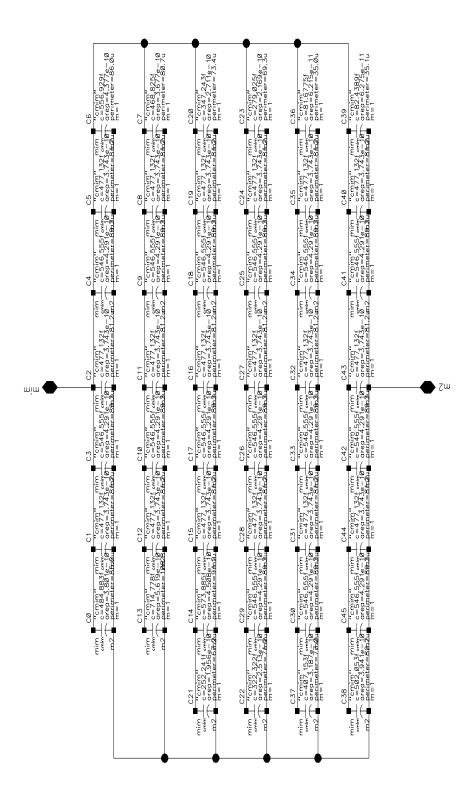

| 21 | <i>n-XYTER</i> front-end schematic; cellname: PRE MIMCAP45                   | 47    |

| 22 | <i>n-XYTER</i> front-end schematic; cellname: PREAMPLIFIER                   | 48    |

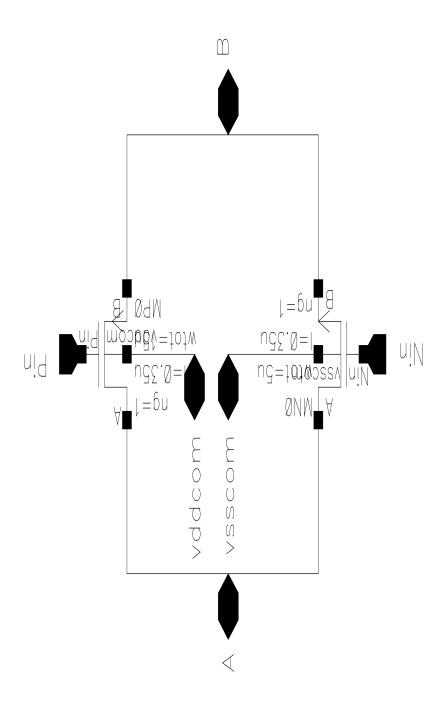

| 23 | <i>n-XYTER</i> front-end schematic; cellname: comp                           | 49    |

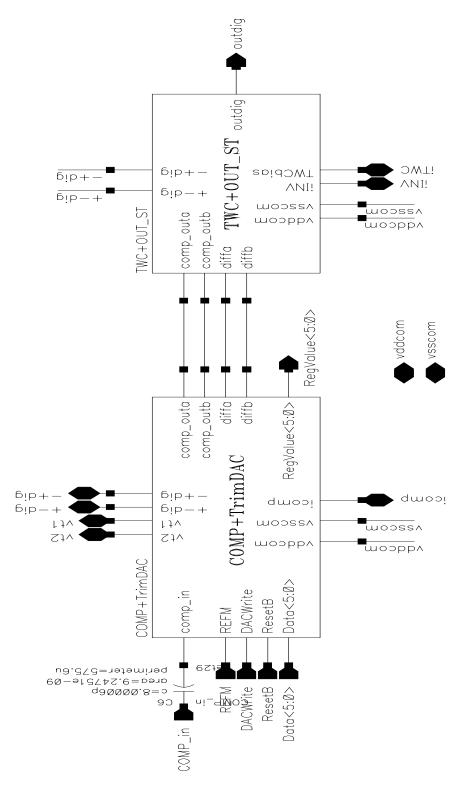

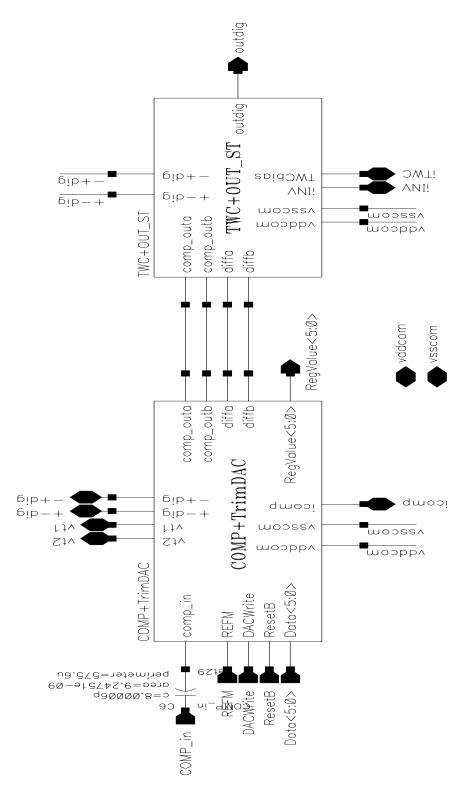

| 24 | n- $XYTER$ front-end schematic; cellname: COMP+TrimDAC                       | 50    |

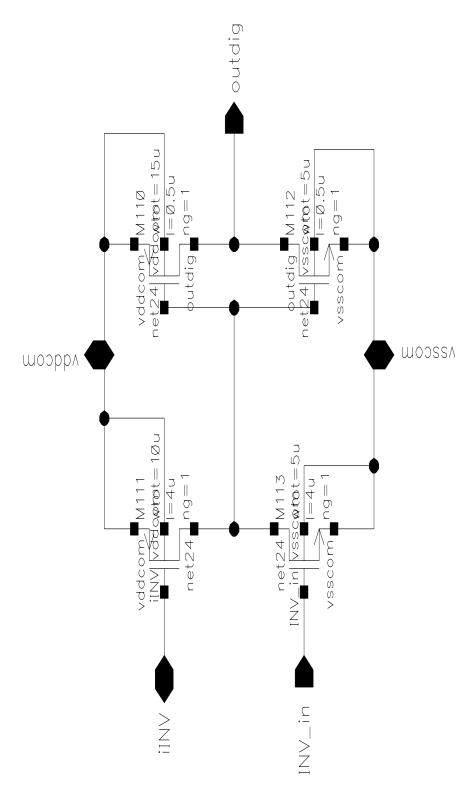

| 25 | <i>n-XYTER</i> front-end schematic; cellname: OUT ST                         | 51    |

| 26 | $n$ - $XYTER$ front-end schematic; cellname: $TG_{}TWC$                      | 52    |

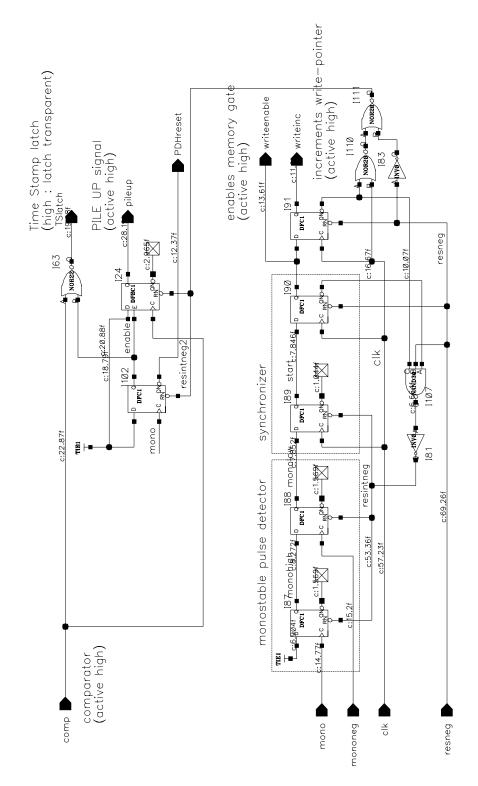

| 27 | <i>n-XYTER</i> front-end schematic; cellname: synchronizer                   | 53    |

| 28 | <i>n-XYTER</i> front-end schematic; cellname: mono-stable                    | 54    |

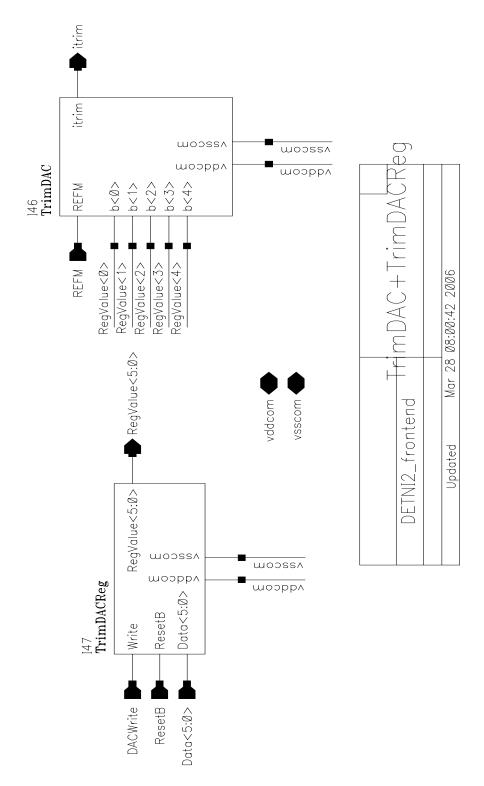

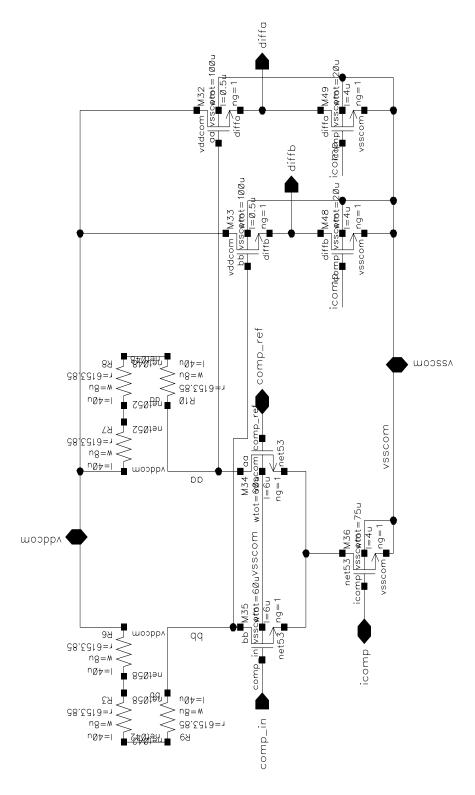

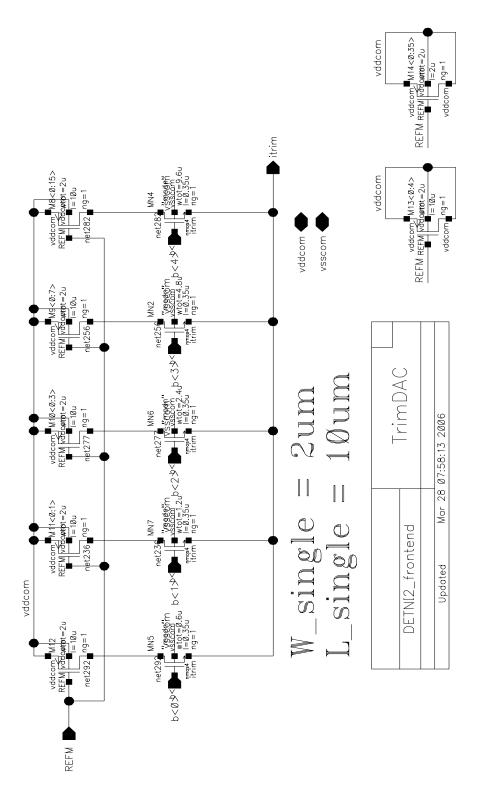

| 29 | n-XYTER front-end schematic; cellname: TrimDAC+TrimDACRe                     | g 55  |

| 30 | <i>n-XYTER</i> front-end schematic; cellname: comp                           | _     |

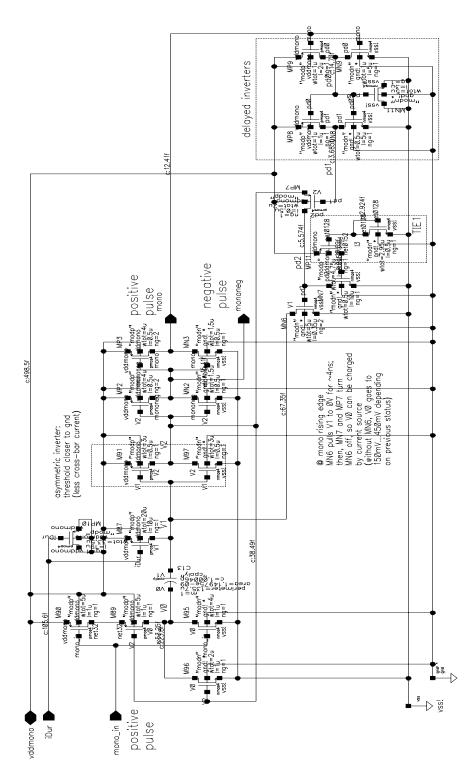

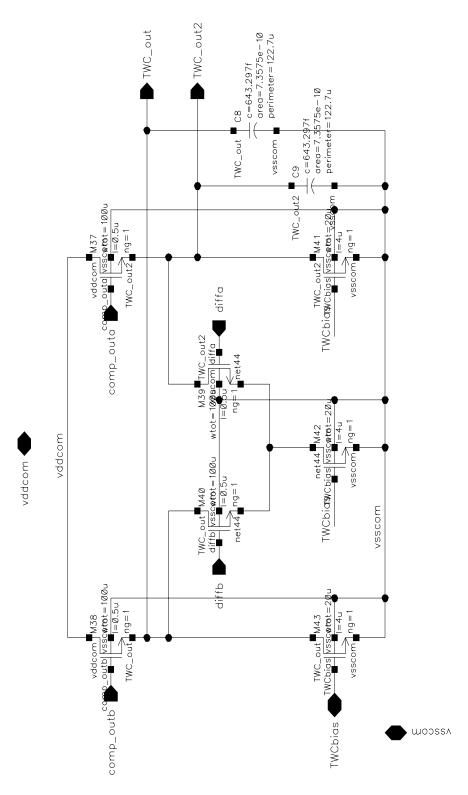

| 31 | <i>n-XYTER</i> front-end schematic; cellname: TWC_var                        | 57    |

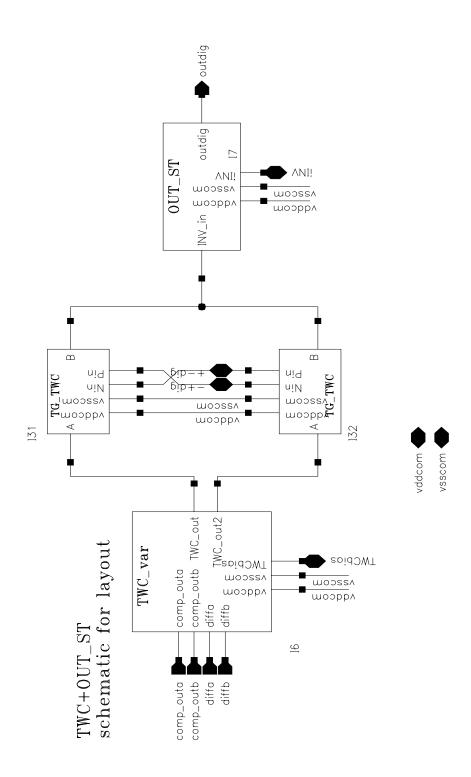

| 32 | n- $XYTER$ front-end schematic; cellname: TWC $+$ OUT ST                     | 58    |

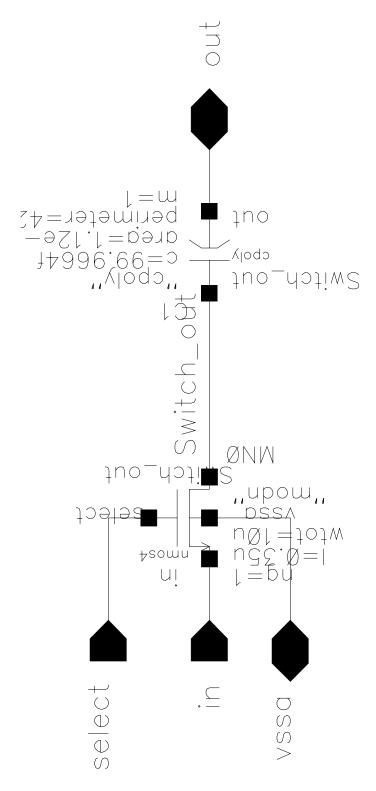

| 33 | <i>n-XYTER</i> front-end schematic; cellname: cal switch                     | 59    |

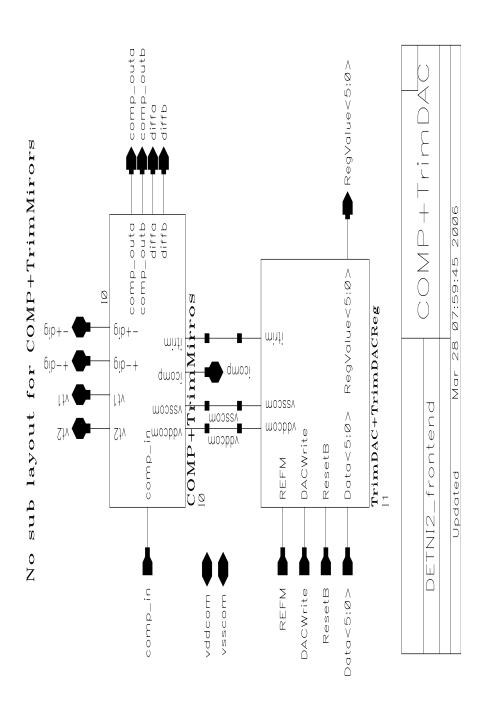

| 34 | n-XYTER front-end schematic; cellname: COMP+TrimMirros .                     | 60    |

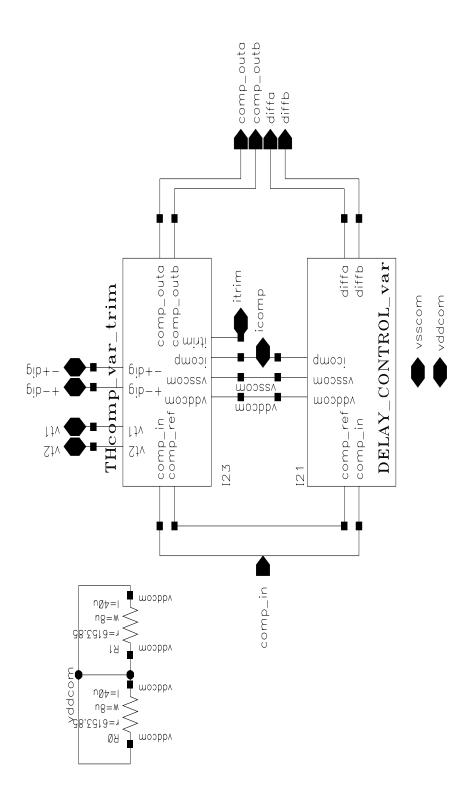

| 35 | n-XYTER front-end schematic; cellname: DELAY CONTROL v                       | ar 61 |

| 36 | n- $XYTER$ front-end schematic; cellname: TrimDAC                            | 62    |

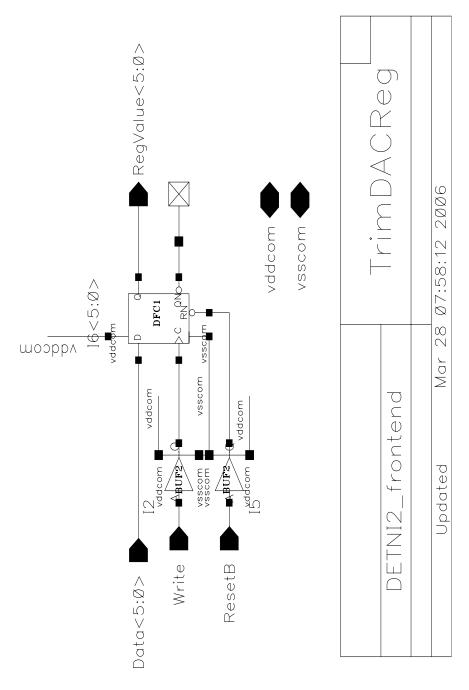

| 37 | <i>n-XYTER</i> front-end schematic; cellname: TrimDACReg                     | 63    |

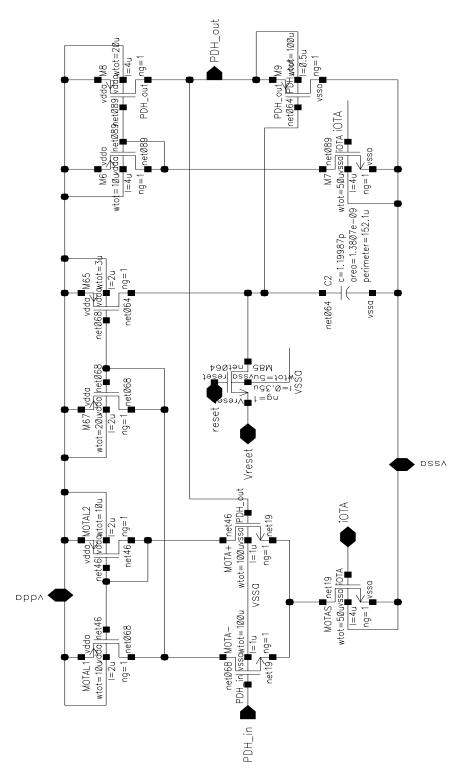

| 38 | <i>n-XYTER</i> front-end schematic; cellname: PDH                            | 64    |

| 39 | <i>n-XYTER</i> front-end schematic; cellname: SLOW2                          | 65    |

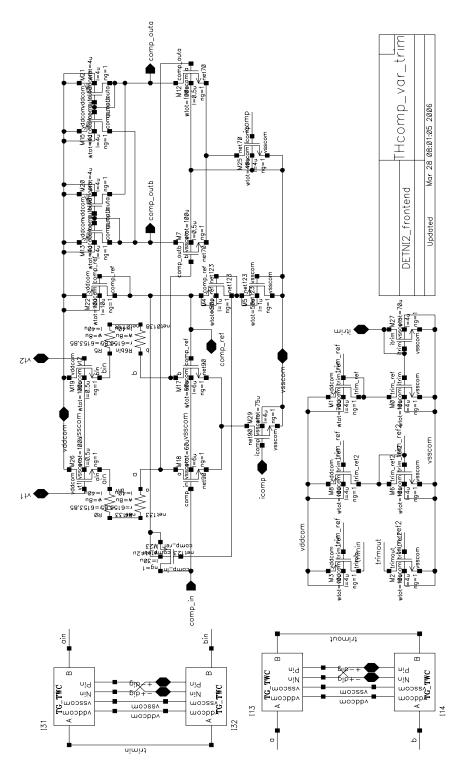

| 40 | n- $XYTER$ front-end schematic; cellname: THcomp var trim .                  | 66    |

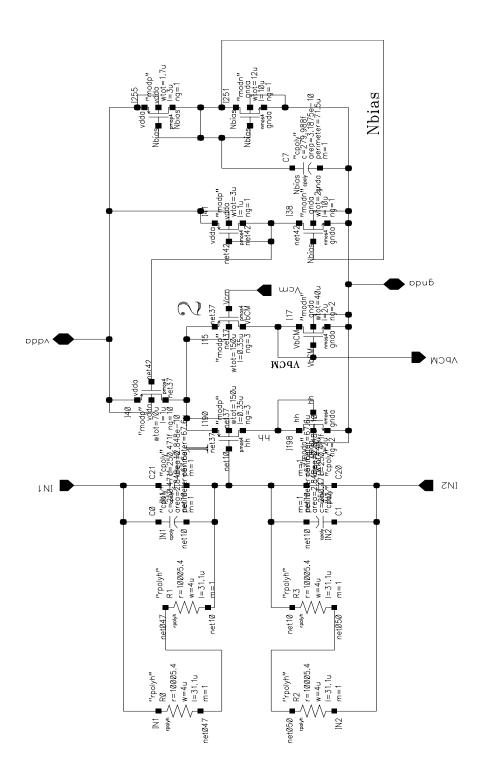

| 41 | <i>n-XYTER</i> front-end schematic; cellname: CMFB                           | 67    |

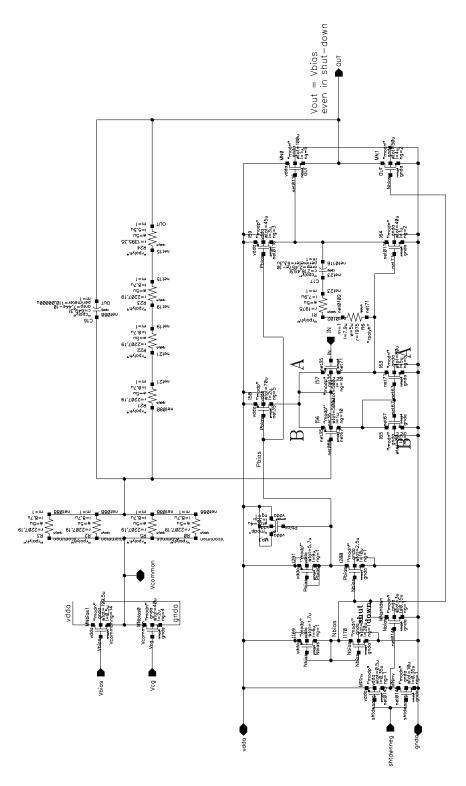

| 42 | <i>n-XYTER</i> front-end schematic; cellname: FAST                           | 68    |

| 43 | n-XYTER front-end schematic: cellname: SLOW1                                 | 69    |

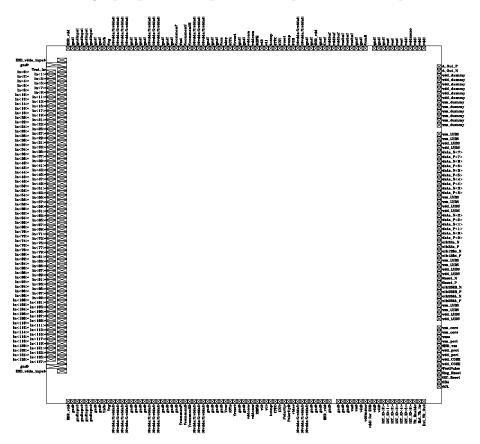

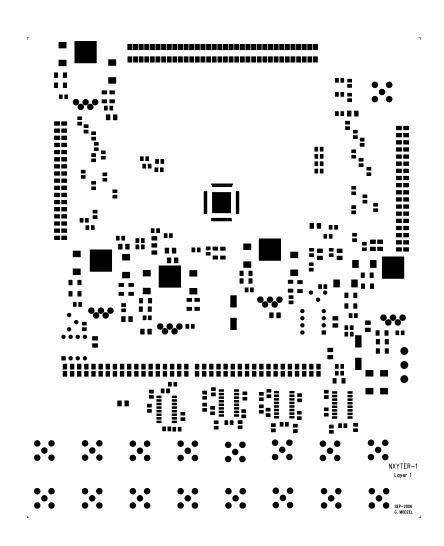

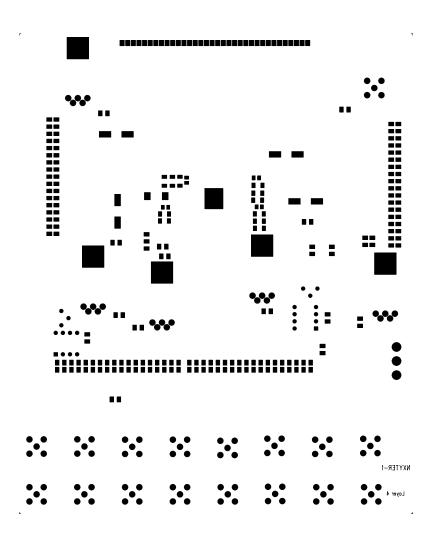

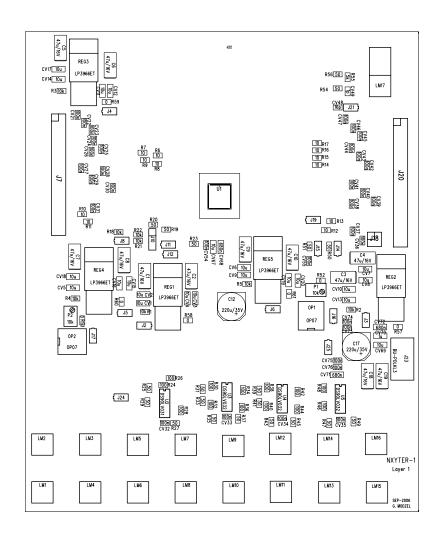

| 44                   | Pad layout of $n$ - $XYTER$ 1.0                                                                                                                      | 70                            |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 45                   | LEFT (input), TOP, RIGHT (out), BOTTOM                                                                                                               | 85                            |

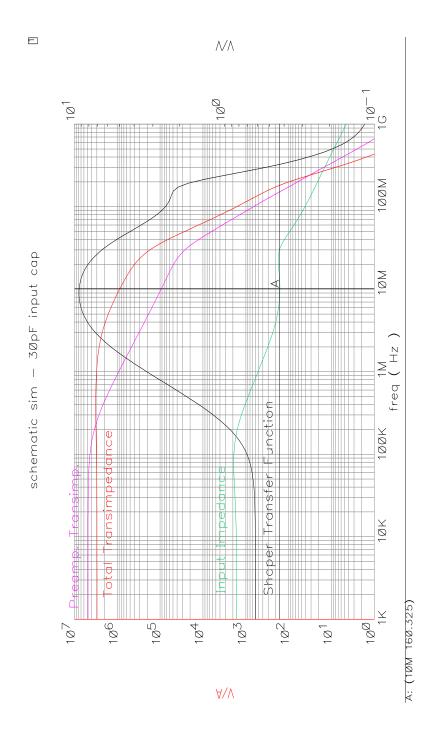

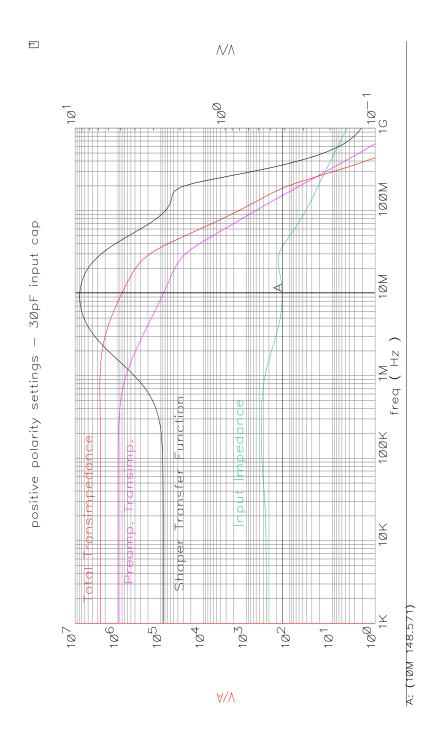

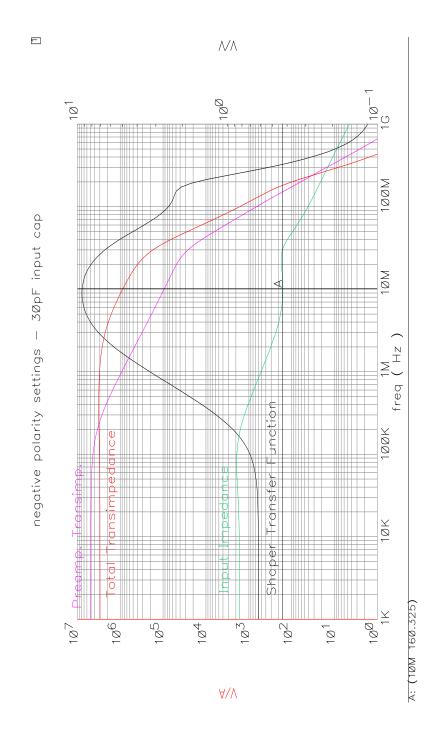

| 46                   | Simplified schematic used in simulations                                                                                                             | 102                           |

| 47                   | Input Impedence vs. frequency, with interchannel coupling effects                                                                                    | 103                           |

| 48                   | Input Impedence vs. frequency for positive input charge setup                                                                                        | 104                           |

| 49                   | Input Impedence vs. frequency for negative input charge setup .                                                                                      | 105                           |

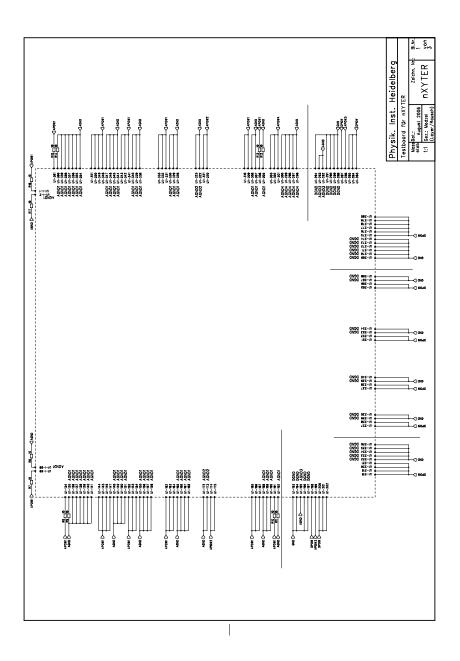

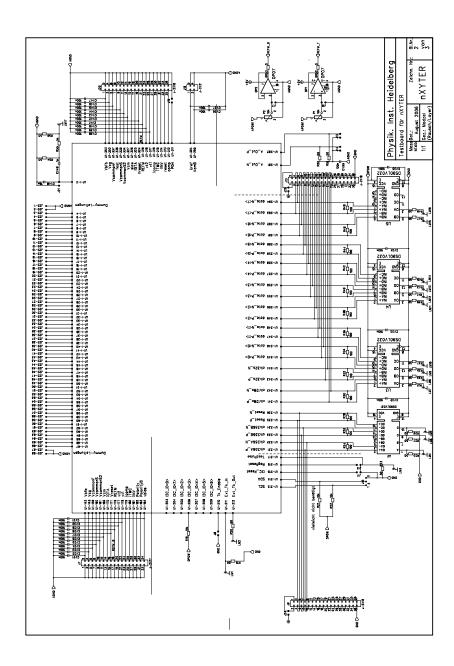

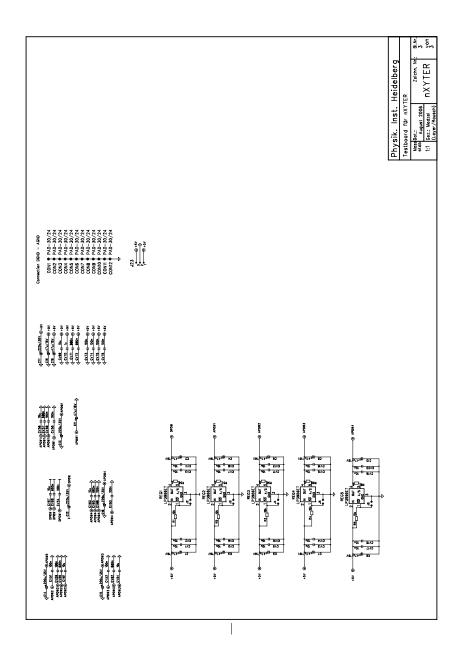

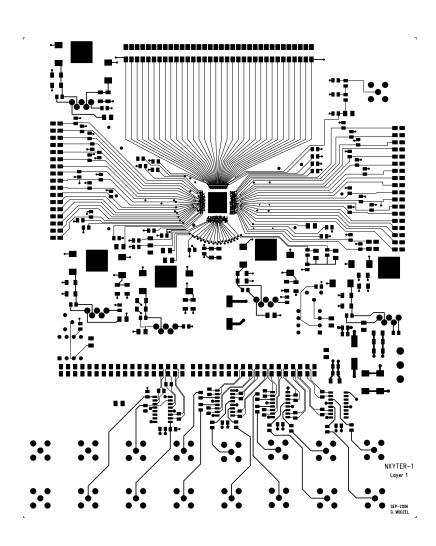

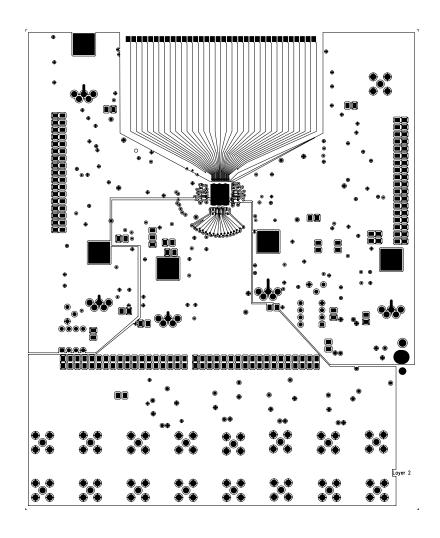

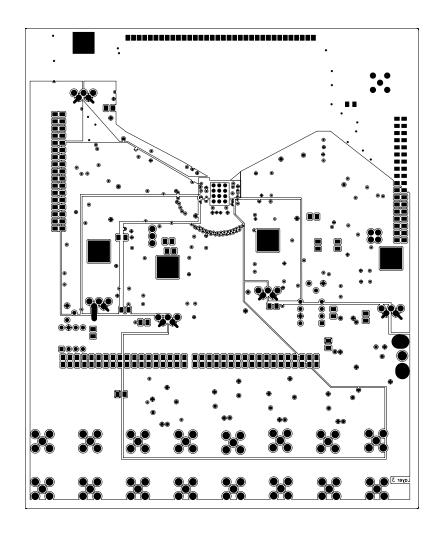

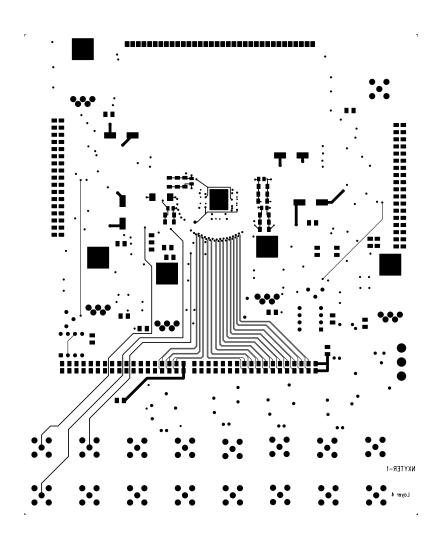

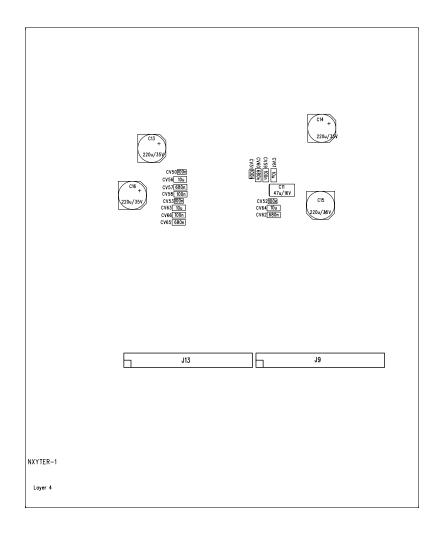

| 50                   | Schematic of the test board (sheet 1 of 3)                                                                                                           | 107                           |

| 51                   |                                                                                                                                                      | 108                           |

| 52                   |                                                                                                                                                      | 109                           |

| 53                   |                                                                                                                                                      | 110                           |

| 54                   | /                                                                                                                                                    | 111                           |

| 55                   | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                                                                                                | 112                           |

| 56                   |                                                                                                                                                      | 113                           |

| 57                   |                                                                                                                                                      | 114                           |

| 58                   | PCB of the test board (solder mask 2 of 2)                                                                                                           |                               |

| 59                   |                                                                                                                                                      | 116                           |

| 60                   | PCB of the test board (components 2 of 2)                                                                                                            | 117                           |

| List                 | of Tables                                                                                                                                            |                               |

| 1                    | Internal register contents for the simulated transient response                                                                                      | 10                            |

| 2                    | DC characteristics of $n$ - $XYTER$                                                                                                                  | 15                            |

| 3                    | Power consumption of the different power nets as current sunk                                                                                        |                               |

|                      | at 3.3V                                                                                                                                              | 16                            |

| 4                    | $I^2C$ Registers                                                                                                                                     | 18                            |

| 5                    | I <sup>2</sup> C Mask Registers                                                                                                                      | 20                            |

| 6                    | Bias and configuration registers of $n$ - $XYTER$                                                                                                    | 23                            |

| 12                   | Digital Output Format                                                                                                                                | 36                            |

| 13                   | Digital Output Format when no data is avaliable from the channels                                                                                    |                               |

| 7                    | Configuration Register 32 (12c address: 32)                                                                                                          | 39                            |

| 8                    | Configuration Register 33 (12c address: 33)                                                                                                          | 40                            |

| 9                    | Adaptation of the front-end to different polarities of input signals.                                                                                |                               |

|                      | N 4 41 4 371 CO 1 1241 CO 1 111 1 1 1 4 4 C                                                                                                          |                               |

|                      | Note that VbiasS2 has little influence. The slow shaper output is                                                                                    | 41                            |

| 10                   | dominated by the dc level of the first stageŠs output                                                                                                | 41                            |

| 10                   | dominated by the dc level of the first stageŠs output Setting the control bits in the registers to control the delay buffer                          | 41                            |

| 11                   | dominated by the dc level of the first stageŠs output Setting the control bits in the registers to control the delay buffer Clock generation modes   | 41<br>41                      |

| 11<br>18             | dominated by the dc level of the first stageŠs output Setting the control bits in the registers to control the delay buffer Clock generation modes   | 41<br>41<br>118               |

| 11<br>18<br>18       | dominated by the dc level of the first stageŠs output Setting the control bits in the registers to control the delay buffer Clock generation modes   | 41<br>41<br>118<br>119        |

| 11<br>18<br>18<br>19 | dominated by the dc level of the first stageŠs output Setting the control bits in the registers to control the delay buffer Clock generation modes   | 41<br>41<br>118<br>119<br>119 |

| 11<br>18<br>18       | dominated by the dc level of the first stageŠs output.  Setting the control bits in the registers to control the delay buffer Clock generation modes | 41<br>41<br>118<br>119        |

# **Document Edition History**

This manual describes the n-XYTER chip versions 1.0, also known as DETNI

| Version | Date       | Author | Description      |

|---------|------------|--------|------------------|

| 1.0     | 2006-06-28 | ASB    | document created |

# Chip Version History

| Version     | Submission Date | Changes relating to previous version |

|-------------|-----------------|--------------------------------------|

| n-XYTER 1.0 | June 2006       |                                      |

# 1 Chip Architecture

The n-XYTER 1.0 is a front-end detector readout ASIC that integrates 128 individual channels and a common sparcifying token-ring digital and analogue interface. It is particularly designed cope with high-speed statistical input signals of poissonian nature. To this end, the front-end part of the chip employs an asynchronous, data-driven architecture in which an analogue signal triggers the registry of a time stamp and the detection of the input signalt's pulse height. In this scheme, time stamp latching is triggered by a time-walk compensated discriminator. Both, the analogue pulse hight as well as the corresponding time stamp are stored into a four level deep fifo as a synchronizing interface.

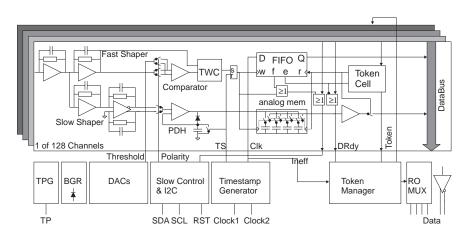

The back-end part of the chip is clock synchronous. It realizes a token ring scheme in which busy channels are read out clock synchronously one after the other. The token ring together with the per channel FIFOs inherently accomplish de-randomization, sparsification as well as readout-bandwidth distribution and bandwidth focusing functions. The system is thus able to process poissonian distributed data at an average per chip data rate of 32 MHz with a maximum of 10% dead time. A simplified schematic is shown in figure 1.

Figure 1: n-XYTER chip architecture. The upper part shows one of the 128 channels. In gray scale behind, more of the independent parallel input channels are suggested. The functional blocks at the lower part depict various controlling blocks of common infrastructure.

#### 1.1 Front End

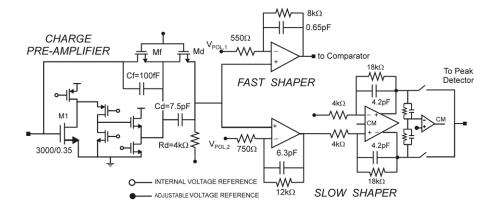

A charge sensitive preamplifier, constructed around a folded cascode circuit forms the input stage. For its superior noise performance, an NMOS input transistor has been chosen. Unlike conventional readout chips, the signal path is split into two branches after the preamplifier:

A fast CR - RC shaper, driving the timing-critical path. This branch serves to generate the time stamp and thus performs the time measurement. The time stamp may later be used to determine the time of incidence of the signal as well as to correlate signals on different channels like for example on the other coordinate in order to determine the eventt's locus in two dimensions.

• A slow  $CR - (RC)^2$  shaper driving the more noise-critical measurement of the deposited energy.

While the fast branch relies on a single-ended topology for the shaper, the slow branch is a two-stage design with a fully differential second stage. This allows the selection of the adequate signal polarity for the subsequent peak detector and hold circuit (PDH) for both polarities of the input signal. The PDH can only take positive input pulses.

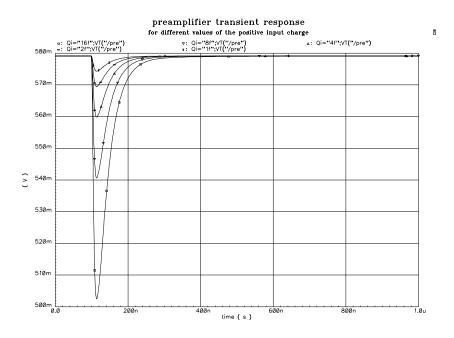

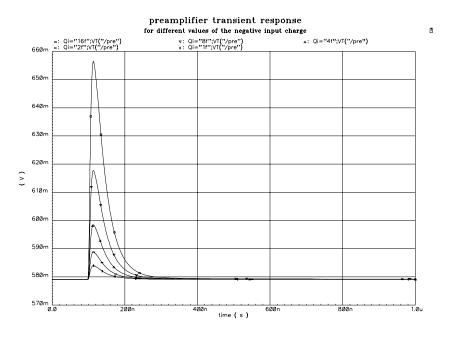

Some frontend simulations show the transient response of all these stages when an input charge of  $\pm$  1 fC,  $\pm$  2 fC,  $\pm$  4 fC,  $\pm$  8 fCor  $\pm$  16 fC is injected into the pre-amplifier. Figures 3 to 6 show the simulated transient response of the analogue front end at different stages in the circuit and for positive as well as negative input charges. The precise transient response does depend upon the values of the internal registers which define the analogue operating conditions. Settings for positive and negative input charge differ in order to maximize the dynamic range within the given clipping margins. Effectively the dc operating level of the fast shaper amplifier output is shifted between 0.56 V and 1.2 V.  $V_{cg}$  is set to 1.4 V and determines the pre-amp bias current,  $V_{bfb} = 0.9$  V controls the pre-amp feedback circuitry and  $V_{cm} = 1.1$  V is the slow shaper's common mode output level. A schematic of the front-end is shown in figure 2.

Figure 2: Schematic of the front-end, including FAST and SLOW shaper branches.

Table 1: Internal register contents for the simulations of transient responses. The register settings determine the values of working parameters for the internal nodes as well as a general configuration.

|        |              | pos.   | neg. input | neg. input   |

|--------|--------------|--------|------------|--------------|

| reg.   | register     | charge | charge,    | charge,      |

| number | name         |        | all ch. on | only testch. |

| 0 -15  | Mask reg     |        | 0          | 0            |

| 16     | $I_{cg}$     |        | 160        | 160          |

| 17     | $I_{cgfoll}$ |        | 255        | 255          |

| 18     | $V_{th}$     |        | _          | _            |

| 19     | $V_{bfb}$    |        | 6          | 0            |

| 20     | $V_{biasF}$  |        | 74         | 95           |

| 21     | $V_{biasS}$  |        | 77         | 125          |

| 22     | $V_{biasS2}$ |        | 100        | 100          |

| 23     | $V_{cm}$     |        | 137        | 137          |

| 24     | cal          |        | -          | _            |

| 25     | $I_{COMP}$   |        | 69         | 69           |

| 26     | $I_{DUR}$    |        | 15         | 15           |

| 27     | $I_{INV}$    |        | 54         | 54           |

| 28     | $I_{PDH}$    |        | 92         | 92           |

| 29     | $I_{TWC}$    |        | 69         | 69           |

| 32     | config 0     |        | 0          | 1            |

| 33     | config 1     |        | 12         | 11           |

Figure 3: Transient response of the pre-amp.

Figure 4: Transient response of pre-amp and fast shaper.

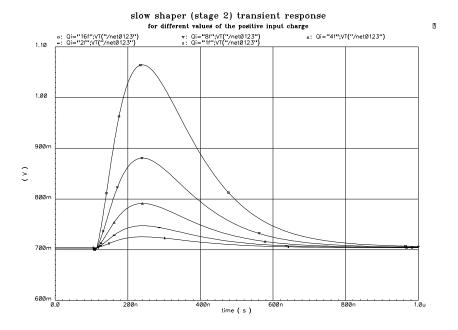

Figure 5: Transient response of pre-amp and slow shaper  $(1^{st} \text{ stage})$ .

14

Figure 6: Transient response of pre-amp and slow shaper chain.

# 2 Electrical Specifications

## 2.1 DC Characteristics

Typical values for the power consumption of the *n-XYTER* chip are given in table 2. Nominal register settings can be found in Table 6. These register settings are intended to give a starting point for optimization. The nominal clock frequency is 250 MHz. It may be altered too, and in particular reduced if desired

Table 2: DC characteristics of n-XYTER

| Supply  | Min.<br>[V] | Nom.<br>[V] | Max.<br>[V] | I<br>[mA] | Description                              |

|---------|-------------|-------------|-------------|-----------|------------------------------------------|

| vdda    | 3.0         | 3.3         | 3.6         | 513       | Positive analogue supply (front-end)     |

| vddmono | 3.0         | 3.3         | 3.6         | 182       | Positive analogue supply (monostable)    |

| vddcomp | 3.0         | 3.3         | 3.6         | 128       | Positive analogue supply (comparator)    |

| vddbuf  | 3.0         | 3.3         | 3.6         | 82        | Positive analogue supply (output buffer) |

| vdd!    | 3.0         | 3.3         | 3.6         | 2         | Digital power supply                     |

These values are estimated from simulations, as well as determined from real consumption of the chip in different operating modes.

## 2.2 Power Dissipation

The data listed in the following section was determined with specific settings for operation chosen: All channels were active, the chip was set for negative input signals. The values are intended to give an impression on the power consumption experienced with the chip experimentally.

| 753  mA                                     |

|---------------------------------------------|

| 359 mA (digital and readout infrastructure) |

| 406 mA                                      |

| 3.15  mA                                    |

| 10.4  mW                                    |

| 12  mW                                      |

|                                             |

Table 3: Power consumption of the different power nets as current sunk at  $3.3\mathrm{V}$

|                    | Vdd    | Vdd   | VDD    | Vdd     | Vdd    | Sum    | Actual            |

|--------------------|--------|-------|--------|---------|--------|--------|-------------------|

|                    | analog | Comp. | Buffer | Digital | Mono-  |        | (total current    |

|                    |        |       |        |         | stable |        | consumption)      |

| 1 power net open   | 589mA  | 115mA | 37 mA  | 99mA    | 10mA   | 850mA  | 764mA             |

| 1 power net closed | 596 mA | 40mA  | 37 mA  | 99mA    | 4mA    | 776 mA | $764 \mathrm{mA}$ |

| (power consumption |        |       |        |         |        |        |                   |

| of the closed net) |        |       |        |         |        |        |                   |

# 3 Operating n-XYTER

## 3.1 Front-end Pulse Shape

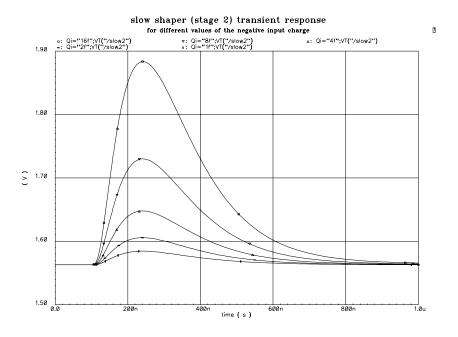

The front-end output signal is a semi-Gaussian pulse which can be characterized through three parameters:

- peaking time  $t_p$  (0 100%) or rise time  $t_r$  (10 90%),

- $\bullet$  peaking voltage  $V_p$  and

- remainder R, which is the ratio between the signal voltage 25 ns after the peak  $(V_{25+})$  and  $V_{\rm p}$ .

The peaking time is sometimes hard to measure since the starting point of the pulse is not well defined, so the rise time  $t_{\rm r}$  (10–90%) is usually quoted. Figure 7 explains the various parameters.

Figure 7: Semi-Gaussian pulse with the corresponding parameters characterizing shape.

The analogue pulse shapes of the n-XYTER readout chip may be observed on the test channel outputs (fast, pad no. 336, and slow, pad no. 326).

The pulse shape can be manipulated by means of 5 bias parameters. For practical operation, three of these are essential, as they control the output signal DC-levels of the pre-amplifier as well as the two shapers:

**Vbfb** sets the preamplifier bias voltage. Higher voltages decrease the rise time and the remainder and increase pulse undershoot.

**VbiasF** defines the shaper dc output voltage level. Increasing voltage shifts the DC-offset to lower values and results in slightly decreasing rise time, remainder and undershoot.

**VbiasS** sets the slow shaper dc output voltage. It does not affect the shape of the pulse, but the DC-offset.

# 4 Configuration and Control of the n-XYTER, Slow Control

n-XYTER contains 46 8-bit registers that may be accessed, programmed and read out via an I<sup>2</sup>C slow control interface. These 46 registers are assigned the I<sup>2</sup>C addresses 00-45. Table 4 coarsely lists and groups these registers in a register-map.

Table 4: I<sup>2</sup>C Registers

| I <sup>2</sup> C Address | Register                                                     |

|--------------------------|--------------------------------------------------------------|

| 0 - 15                   | Mask registers                                               |

| 16 - 29                  | Analogue bias and analogue front-end configuration registers |

| 30 - 31                  | spare                                                        |

| 32 - 33                  | General configuration register                               |

| 34 - 35                  | Overflow counter, readonly, reset after readout              |

| 36 - 37                  | Missing token counter, readonly, reset after readout         |

| 38                       | Test pulse delay register                                    |

| 39                       | Test trigger delay register                                  |

| 40                       | spare                                                        |

| 41                       | spare                                                        |

| 42                       | Trim DAC shift register (bit 04),                            |

|                          | channel shut down on bit 5                                   |

| 43 - 45                  | Clock delay registers                                        |

## 4.1 I<sup>2</sup>C Interface

The chip's slow control interface is a standard  $I^2C$ -slave device featuring a transfer rate of  $100\,\mathrm{kbit/s}$ . The chip address, necessary to access a single device via the  $I^2C$ -bus, is 7 bits wide and assigned via the address pads  $I2C\_ID<6:0>$  (c.f. section B.3). The n-XYTER chip may be given any address in the range 8-119. The addresses 0000XXX and 1111XXX are reserved in the  $I^2C$ -standard for other purposes [3].

The internal registers may be accessed via a pointer register. It contains the address of the register to be written or read first. Only the 6 least significant bit (LSB) of the pointer byte are evaluated. The pointer is internally incremented by 1 after each transferred data frame (auto-increment). In this way registers with adjacent addresses may be accessed consecutively. The pointer register itself remains unchanged, i.e. a new transfer will start at the original pointer position. Figure 8 explains the transfer sequences in write and read mode. Data is always transferred with the most significant bit (MSB) first. In write mode, the chip address is transmitted after initializing the transfer, followed by the pointer byte and the data. After transmission of one data frame, the pointer addresses the subsequent register because of its auto-incrementing function. Transfer of the pointer byte is obligatory in write mode.

In read mode there are two versions:

#### • Preset pointer

After initializing the transfer and sending the chip address, data is immediately read out. The pointer has been set in a previous transfer.

Pointer set followed by immediate read-out

After initializing the transfer and sending the chip address the pointer

byte is transferred. The I<sup>2</sup>C-bus is re-initialized, the chip address is sent

and data is read out.

### Write mode Single addressing R/W General call addressing Master address Read mode Preset pointer XXX XXX Р R/W Data Pointer set followed by immediate readout R/W XXX from master to slave from slave to master

Figure 8:  ${\rm I^2C}$ -bus write and read sequences for accessing slow control registers on the n-XYTER .

Caveat: In this version of the n-XYTER, the auto-increment function of the  $\rm I^2C$  is not adequately adapted: Upon writing, auto-increment is turned off for or passing registers 28 and 29. Additionally, auto increment is operative only on a maximum of 64 addresses, which however is not relevant for the chip discussed in here. Upon reading, auto-increment does work for all register addresses up to 46. These issues may be entirely avoided if registers are individually addressed, thus avoiding auto-increment features.

Commercially available  $I^2C$ -devices usually operate at 3.3 V or 5 V. Because the n-XYTER is a 3.3 V circuit it is necessary to use an adapter to operate with 5 V. A simple FET level-shifter with local bus pull-ups to the respective operating voltage level on either side may be employed.

The following subsections list the registers with their physical range, resolution, nominal setting and power up default settings.

#### 4.1.1 Mask Registers

The Mask Register is a 128 bit length register which is accessible in parts of 8 bits width via the  $I^2C$  registers 0 to 15 as shown in Table 5. In particular, the channels from 0 to 7 are masked by bits from 0 to 7 of register 0 and channels from 120 to 127 are masked by bits from 0 to 7 of register 15. When a channel is masked the corresponding bit is set to 1, the output of the front-end does not propagate to the back-end and no event is registered at the output in any mode of operation.

Table 5: I<sup>2</sup>C Mask Registers

| Reg. No | Description           |

|---------|-----------------------|

| 0       | Mask channels 7-0     |

| 1       | Mask channels 15-8    |

| 2       | Mask channels 23-16   |

| 3       | Mask channels 31-24   |

| 4       | Mask channels 39-32   |

| 5       | Mask channels 47-40   |

| 6       | Mask channels 55-48   |

| 7       | Mask channels 63-56   |

| 8       | Mask channels 71-64   |

| 9       | Mask channels 79-72   |

| 10      | Mask channels 87-80   |

| 11      | Mask channels 95-88   |

| 12      | Mask channels 103-96  |

| 13      | Mask channels 111-104 |

| 14      | Mask channels 119-112 |

| 15      | Mask channels 127-120 |

#### 4.1.2 Bias Registers

Registers 16-29 are bias registers that serve to tune and control the analog frontend stages. Apart from general best settings that need no repeated optimization for most parameters, the parameters **VbiasF** and **VbiasS** as well as **Vbfb** need to be set upon a change of the polarity of the input pulses that are to be detected:

$\mathbf{Icg}$  (16) (named  $\mathbf{Vcg}$  in the schematic): This is a pre-amplifier parameter that ...

Icgfoll (17) (named Vcgfoll in the schematic) sets the bias voltage for the shaper (together with VbiasF) and both stages of the slow shaper (together with VbiasS and VbiasS2 in this case). For more information about these voltages check the paragraphs on VbiasF, VbiasS and VbiasS2.

Vth (18) sets the global threshold voltage for the comparators, i.e. it defines the pulse strength that is necessary to trigger the comparator. Two voltages are created for positive and negative input charge: vt1 and vt2. These discriminator input voltages are selected depending upon the front-end polarity setting in configuration register number 33, bit 2.

**Vbfb** (19) Sets the discharge time for the preamplifier by controlling the resistance of the transistors Mfb and Mpz. Vbfb is also the upper limit for the output voltage. A large negative charge as input produces a large positive output signal that might be cut through if Vbfb is set too low. Nevertheless, increasing Vbfb will decrease the discharge resistance and result in greater noise and undershoot. It also decreases the rise and discharge time.

VbiasF (20) sets the bias voltage for the fast shaper (together with Icg). It serves to set VcommonF, and thus modifies the dc offset of the shaper output. The potential of VcommonF may be observed at the respective test pin. VcommonF is connected over the two packages of resistors RcFa (R0, R5, R2, R3) and RcFb (R21, R22, R23, R24) and a capacitance (C16) to the output of the fast shaper. A change in VcommonF is reflected in the output with the following multiplier: 1 + (RcFb/Rcfa) = 17. So the fast shaper is very sensitive to pickup in VcommonF. VbiasF should be used to adjust the bias voltage of the output. For a negative input charge the resulting signal is positive and its bias should be around 0.5 V so that there is enough space for the upward swing. For a positive input charge the signal is negative and its bias should be around 1.2 V so there is enough space for a downward swing.

VbiasS (21) sets the bias voltage for the first stage of the slow shaper (together with IcgFoll). It also sets VcommonS, which can be measured at the respective test pin. The working principle is exactly as with VbiasF, even the multiplier is identical. Only the bias value of the output (of the first stage of the slow shaper) is different.

VbiasS2 (22) together with IcgFoll sets the bias voltage for the second stage of the slow shaper. It also sets VcommonS, which can be measured at the respective test pin and should be identical with the input bias voltage (which is the output of the first stage of the slow shaper). Since this cannot be measured the following can be used: If they are identical, the second stages slow shapers output bias voltage is identical for positive and negative charges. A difference can also be caused by a wrong setting for Vcm/Vbase.

Vcm/Vbase (23) : The output of the slow shaper is differential. Vcm/Vbase adjusts the target voltage of the common mode feedback that stabilizes the output. It should be the same as the bias voltage of the output of the slow shaper second stage.

cal (24) : If the chip is in "test pulse mode" (c.f. configuration reg. 32, bit 0), an internal pulse can be created and fed to the analog channels, thus enabling testing of the chip without external input. Register 'cal' sets the strength of this pulse.

iCOMP (25) sets the current for the main stage of the comparator.

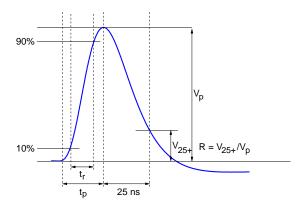

**iDUR** (26) adjusts the dead-time of the analog channels, i.e. the minimal time difference between two events so that both will be distinguished as two signals on one channel. Upon occurance of a new trigger piling up on a previously registered signal within the pre-defined dead time, only one signal will be registered, where the analogue pulse height must be considered contaminated. This data element is then marked as "pile-up".

This timing logic is realized by means of a mono-stable, which is activated through the trigger signal. iDur sets the discharge current and thus the time-window width of the mono-stable, which in turns arms a watchdog-logic to check for a coincidence during this time span. The larger the programmable current

Figure 9: Variable dead time and its resolution as a function of the iDur parameter

iDur, the shorter the window.

The width of the time window is given by:

$$T_{dead}[ns] = \frac{4790}{DAC} + 250 + (31.25 \text{ synchronization jitter})$$

Since the dead-time is an adjustable parameter, it may be employed to study signal saturation and detector performance. Note though, that the dead-time introduced here must be considered non-re-triggerable dead-time.

iINV (27) sets the current in the output stage of the comparator.

iPDH/iOTA (28) sets the current in the peak detect and hold circuit.

iTWC (29) sets the current in the time walk compensation circuit.

#### 4.1.3 Configuration Registers 32 and 33

The Configuration Register are two successive 8 bit registers accessible trough the  $I^2C$  registers 32 and 33. Tables 7 and 8 describe how they control the internal configuration of the chip.

#### 4.1.4 Overflow Counter, Registers 34 - 35

The diagnostic overflow counter contains the current number of the events lost due to FIFO overflows since the last reset of the counter. The Overflow counter

Table 6: Bias and configuration registers of n-XYTER.

| Table 0. Dias and configuration registers of 16-24 Figure |            |                      |                      |                      |         |                       |  |  |  |  |  |

|-----------------------------------------------------------|------------|----------------------|----------------------|----------------------|---------|-----------------------|--|--|--|--|--|

| Reg.                                                      | Reg. Name  |                      | Resol. Nominal       |                      | Setting |                       |  |  |  |  |  |

| _                                                         |            | Range                | of                   | of Value             | Reg.    | Description           |  |  |  |  |  |

| no.                                                       | _          | _                    | LSB                  | varue                | content |                       |  |  |  |  |  |

| 16                                                        | Icg        | 128 - 270 μΑ         | 0.573 μΑ             | 187 μΑ               | 114     | bias current          |  |  |  |  |  |

| 17                                                        | Icgfoll    | 0 - 214 µA           | 0.835 μΑ             | 124 µA               | 151     | source follower bias  |  |  |  |  |  |

|                                                           | 30         | •                    | •                    | •                    |         | current               |  |  |  |  |  |

| 18                                                        | Vth        | (vdd) - (vdd-862 mV) | $3.42\mathrm{mV}$    | —μA                  |         | comparator thresh-    |  |  |  |  |  |

|                                                           |            |                      |                      |                      |         | old voltage           |  |  |  |  |  |

| 19                                                        | Vbfb       | 0.928 - 1.851 V      | $3.66\mathrm{mV}$    | 1.2V                 | 80      | preamplifier voltage  |  |  |  |  |  |

| 20                                                        | VbiasF     | 0.928 - 1.85 V       | $3.73\mathrm{mV}$    | 1.27V                | 103     | fast shaper voltage   |  |  |  |  |  |

| 21                                                        | VbiasS     | 1.031 - 1.640 V      | $2.55\mathrm{mV}$    | 1.27V                | 113     | slow shaper voltage   |  |  |  |  |  |

| 22                                                        | VbiasS2    | 1.031 - 1.640 V      | $2.51\mathrm{mV}$    | 1.129V               | 44      | slow shaper voltage   |  |  |  |  |  |

| 23                                                        | Vcm, Vbase | 0.825 - 1.581 mV     | $2.97\mathrm{mV}$    | 1.1V                 | 103     | common mode volt-     |  |  |  |  |  |

|                                                           |            |                      |                      |                      |         | age                   |  |  |  |  |  |

| 24                                                        | cal        | 1.381 - 3.00 V       | $-6.35\mathrm{mV}$   | 2.0V                 | 100     | voltage calibration   |  |  |  |  |  |

| 25                                                        | iCOMP      | 0 - 214.2 μΑ         | 0.843 μΑ             | 62.1 μΑ              | 62      | current bias for com- |  |  |  |  |  |

|                                                           |            |                      |                      |                      |         | parator               |  |  |  |  |  |

| 26                                                        | iDUR       | 0 - 65.4 μΑ          | $0.657\mu\mathrm{A}$ | $0.657\mu\mathrm{A}$ | 15      | current bias          |  |  |  |  |  |

| 27                                                        | iINV       | 0 - 260.1 μΑ         | 1.02 μΑ              | 37 μΑ                | 37      | current bias          |  |  |  |  |  |

| 28                                                        | iPDH, iOTA | 50.5 - 139.2 μA      | 0.349 μΑ             | 80 μΑ                | 92      | current peak detector |  |  |  |  |  |

| 29                                                        | iTWC       | 0 - 214.2 μΑ         | 0.843 μΑ             | 60 μΑ                | 75      | current time walk     |  |  |  |  |  |

|                                                           |            |                      |                      |                      |         | compensation          |  |  |  |  |  |

| 30                                                        | reserved   | -                    |                      |                      |         |                       |  |  |  |  |  |

| 31                                                        | reserved   | =                    |                      |                      |         |                       |  |  |  |  |  |

is a 16 bit register accessible thought I<sup>2</sup>C registers 34 and 35. These are read only registers and are reset after read. The reset is synchronous with reading, once 8 bits are read, they are set to 0 (all bits are 0). After 2 readings (consecutively on register 34), all bits are set to 0.

# 4.1.5 Missing Token Counter, Registers 36 - 37

This diagnostic counter contains the current number of tokens lost since the last reset. The Missing Token Counter is a 16 bit register accessible trough the I<sup>2</sup>C registers 36 and 37. These are read only registers and are reset after read. The reset is synchronous with reading. Once 8 bits are read, they are set to 0. After 2 consecutive readings on register 34, all the bits are set to 0.

# 4.1.6 Trim DAC Shift Register 42: Local Threshold and Individual Channel Shut-Down

The Trim-DAC Register may be employed to equalize the offset and gain mismatch of effective local thresholds. For every channel, a 5 bit corrective adjustment value may be tuned to add to the global threshold. Additionally, register 42 provides a switch to individually shut-down any one or more front-end channel.

The implementation consists of a 129 stage shift register, one for each channel. Each channel has its corresponding 1 byte local register with bit 0 to 4 controlling local threshold correction and bit 5 being the channel shut-down bit (bit 5 being the channel shut-down bit  $\frac{1}{2}$ ).

Figure 10: Shift register principle

#### = 1 shuts off the channel).

A write command on register 42 addresses the first one of the chain, the location of channel 127. A read command on register 42 reads from the very last item, the position of the test channel, which is located just next to input channel 0. To set the values of the DACs, a sequence of 129 writing commands to register 42 needs to be send. Each writing pushes another 8 bits into the shift register, where previous values are pushed through to successive channel numbers. In order to read the entire shift register, 129 alternating read- and write-actions must be performed. The first one read will correspond to the test channel, no. 129, the last one to channel no. 1 respectively.

If e.g. location number 50 is to be read out while maintaining the content of the shift registers, the entire shift register needs to be read out by alternating read and write commands to register 42, that write back the very value just read out. The principle of the shift register is shown in Figure 10.

Upon bit 5 set to 1 in the Trim-DAC register of any channel, power in the respective channel is cut off from the pre-amplifier, the fast shaper, the first stage of the slow shaper as well as the second stage of the slow shaper. Figure 20 and the successive schematics of the hierarchy in Appendix ?? show the electrical connections of the shtdwnneg signal which is controlled through bit 5 of the shift register entries.

#### 4.1.7 Delay Registers

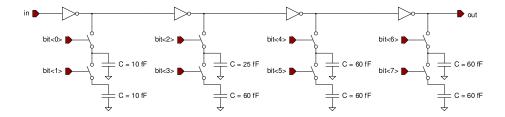

Signal delays may be introduced and controlled in various locations of the circuit. Such delays are programmed via I<sup>2</sup>C delay registers. Registers 43, 44 and 45 are used for the clocking scheme. Registers 38 and 39 are used to shift test signals in dedicated test modes with respect to the clock. These delay registers are inverter based delays as depicted in figure 11 and have a typical delay of about 100 ps per bit. Note that the effective delay is asymmetric between a rising and a falling edge. The internal structure of the delay buffers is presented in figure 11. The effective delay of the buffer may be programmed by attaching capacitive loads to the outputs of four serially connected inverters. Note that pairs of capacitors are connected serially to optimize minimum delay of the

buffer. Thus setting e.g. bit 1 while bit 0 is not asserted does not alter the delay!

Figure 11: Simplified schematic of the delay buffer

The expected delay can be calculated with the following equations:

$$Falling\ Output = \frac{0.01\ ns + 2.00\ ns}{pF} \cdot C[pF]$$

Rising Output =

$$\frac{0.21 \ ns + 1.71 \ ns}{pF} \cdot C[pF]$$

$$Average = \frac{0.11 \ ns + 1.86 \ ns}{pF} \cdot C[pF]$$

Falling Output is the logic transition from high to low and C is the load capacitance at the output of the inverter.

Rising Output is the logic transition from low to high and C is the load capacitance at the output of the inverter.

Average is the average value expected for a transition (from low to high or high to low) and C is the load capacitance at the output of the inverter.

The entire delay module consists of 4 inverters

$$td = \frac{0.44 \ ns + 1.86 \ ns}{pF} \cdot C_{tot}[pF]$$

where td is the total delay and  $C_{tot}$  the sum of all the load capacitance at the output of the inverters.

The plot in Figure XX, (from test measurements) shows the relationship between delay settings programmed into the registers and the resulting time delay between the clock phases. This measurement can be used to calibrate the delay and archieve proper time settings.

**Test Pulse Delay Register 38** The test pulse delay register controls the delay of test pulse injection with respect to the clock, if clock synchronization is selected for the test pulse mode in configuration register 32, bit 1.

Test Trigger Delay Register 39 The test trigger delay register controls the delay between test triggering of the front-end's output and data registry and the clock if clock synchronous mode is selected in configuration register 32 bit 4. (C.f. figure 12.)

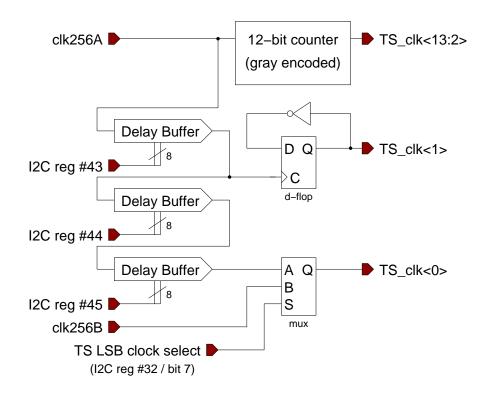

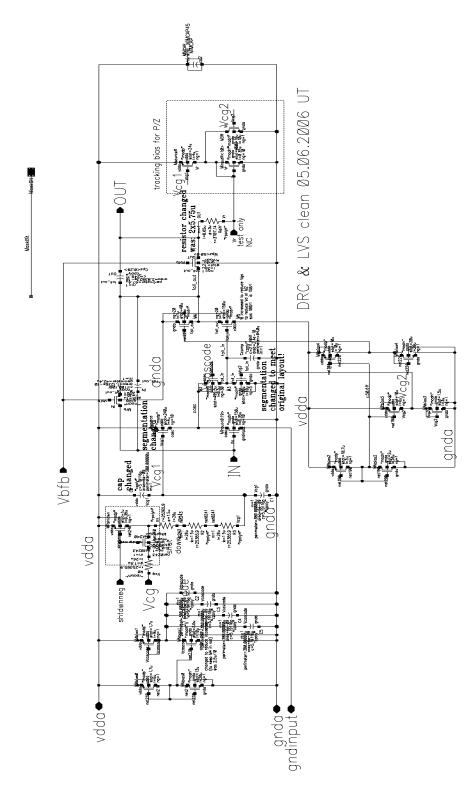

Clock Delay Register 43 The clock fed into the chip on the input clkA is split into two clock branches. This register controls a shift in time of the second clock branch with respect to clkA. It needs to be tuned to cause a phase shift of 90°between the two branches (See the diagram in figure 16). The delayed signal feeds into a D-flip-flop and is employed as gray coded time-stamp bit number 1.

**Clock Delay Register 44 and 45** The output clock of Delay Register 44 is also fed successively into clock delay registers 44 and 45. Here the delays are chosen so that a real, homogeneous gray code is realized.

## 4.2 Signal Polarity Configuration

The n-XYTER may be configured to alternatively detect signals of positive or negative polarity.

Since the peak detector to which the energy signal is fed after the slow shaper may only analyze pulses of one polarity, the preceding second stage of the slow shaper is realized as an entirely differential circuit. Likewise, the discriminator that is fed from the fast shaper circuit, is realized entirely differential, so that depending upon the polarity of the connecting branch, either positive or negative signals may be discriminated or peak analyzed. The choice of the input channels of these differential internal circuits is controlled through bit 2 of Configuration Register 33. It controls the switches depicted in figure 1.

Front-end polarity select (bit 2 of Configuration Register 33)

- When **0**: Switch configuration for **negative** input charge.

- When 1: Switch configuration for **positive** input charge.

Additionally, the front-end should be adapted for maximum dynamic range: Here configuration merely comes down to an adjustment of DC-operating levels that allow to exploit the entire analogue operating window for unipolar signals. To this end, the adjustable nodes in 2 may be set by means of I<sup>2</sup>C registers. In particular the parameters VbiasF, VbiasS and VbiasS2 as well as Vcgfoll are employed to set VcommonF, VcommonS and VcommonS2, the nodes depicted as adjustable in figure 2. VbiasS2 does however have little influence on the output dc level as compared to VbiasS. This is due to the fact that it is primarily the first stage that introduces gain in this shaper. Finally, Vbfb is adjusted as to optimize the pre-amplifier feedback time constant while keeping Johnson noise from the feedback resistance minimal. For positive and negative signals, the optimum shows slightly different values as in the Paul O'Connor dynamic pole zero circuit employed, the feedback resistance is modified by the signal level itself.

#### 4.3 Test Channel

In addition to the 128 channels, the *n-XYTER* chip integrates a *test channel* that allows direct access to it's front-end's shaper outputs fast, pad no. 336, and slow, pad no. 326, as well as the comparator output comp, pad number 312. An input charge can be injected either via the test channels input port Test\_In (pad no. 3) or via the internal test pulse generator in test pulse mode and addressing calibration group 11 (cf. 4.6). Additional connections Vbfb on pin 142 and 353, icomp on pin 179 and 316, iINV on pin 314 and Uref on pin 304 are also accessible to monitor or force an appropriate bias to the test channel. Please not that the dynamic output signals of the test channel shapers, and in particular the fast shaper, are not buffered. They need to be sampled with an oscilloscope probe of less than 1 pF input capacitance. Even connecting pobtraces need to be designed for absolute minimum capacitance.

#### 4.4 Channel Shutdown

The analog channel has a shutdown function which cuts off the power supply for the front-end, the fast shapers, the first stage of the slow shaper and the second stage of the slow shaper. It is not possible to switch off the individual components of a channel but the entire front-end at once. Figure 20 in appendix A shows the electrical connections of the shtdwnneg signal.

The channel is switched off individually, regardless of the on/off status of the adjacent channels. The shutdown is activated by writing a logic 1 in the trimdac register 42, bit number 5. The first entry of this shift register after writing to it 129 times controls the test channel. Thus the state of the test channel shift register entry is the first that is read out. The ordinary 128 channels are addressed and read out by successively writing into the shift register, entry 2 corresponds to channel 0 and entry 129 corresponds to channel number 127.

#### 4.5 Reset Modes

Three different types of resets exist on the n-XYTER.

- Time Stamp generator reset pins 235/236 Reset\_PN is an LVDS signal that asynchronously resets the time stamp generator. The counter of the timestamp is initialised to value 0 which means all bits are zero. The pulse width (a transition from low to high and then back to low) must be longer than 350 ps. This reset signal also serves to reset the down counter which is used to generate the lower frequency signals 128 MHz and 32 MHz. For adequate operation of these data transmission clocks and in particular their relative phases and the phases with respect to the time stamp, a time stamp generator reset must be applied prior to operation.

- *I*<sup>2</sup>*C* reset is controlled by the I2C\_Reset on pin 215. When active (it is active low), this signal resets the internal digital I<sup>2</sup>C logic and the state machines, but not the values loaded in the I<sup>2</sup>C registers. The contents of the registers 0 to 45 are preserved and their values do not change after activating this reset. It is recommended to apply the signal, being internally asynchronous, longer than one clock period.

• *I*<sup>2</sup>*C* registers reset is controlled by the RegReset on pin 216. When active (it is active low) this signal resets all the registers of the I<sup>2</sup>C. In this situation all registers are set to their default values. Hard wired default values are either 0 or 128.

#### 4.6 Test Modes

The n-XYTER may be set to four different states of operation that are selected by means of bit 0 (test pulse enable) and bit 3 (test trigger mode) in the control register number 32.:

- With both bits inactive, 0, ordinary operation is selected. The discriminator signals of all unmasked channels are fed forward and processed.

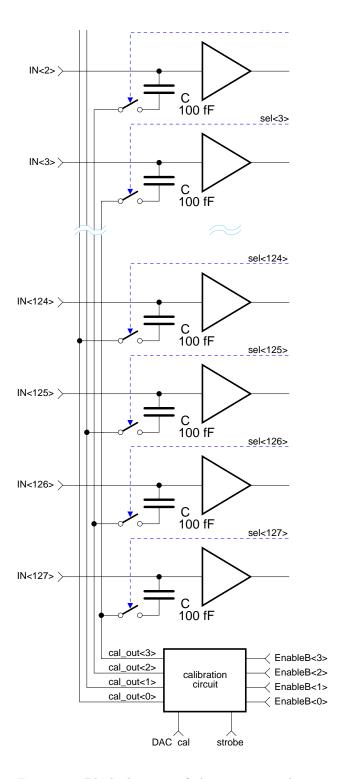

- "Test pulse enable" enables the injection of test pulses into one of four groups of 32 channels (selectable through control register no. 33 bit 0 and 1). In this test mode #0) or "test pulse mode", an external digital, single ended signal on the input "TestPulse" (pad 217) triggers the injection of test pulses if the control bit "test pulse enable" is selected. The generated signal is further processed just like an ordinary detector signal (see figure ??). In this case, the mask register serves as a select register to close the switches at the inputs of selected channels (mask bit set to 1) so that the test pulse is coupled through a 100fF coupling capacitance into the respective channel input (see figure 13. It may be employed to mimic a detector signal where the precise time of injection is under control and directly correlated to the time of application of the external TestPulse signal. This test mode is further discribed in chapter 4.6

- If on the other side test trigger mode (or test mode #1) is chosen through control bit 3 reg. 32 set to 1, analogue front-end discriminator signals are inhibited from passing on to the digital readout. Here, the internal signal "test trigger" in figure ??, likewise triggered by the external signal Test-Pulse, emulates a trigger signal on all unmasked channels. On the rising edge, the digital trigger and the time stamp registry is forced. Further, the peak detector is activated on these channels to sample the analogue energy signal. On the falling edge of the external TestPulse, the momentary states of the discriminators are latched into a register that is mirrored onto the mask register read addresses. The precise time of the sample may thus be controlled through the length of the TestPulse digital signal. This test-mode emulates simultaneous firing of many (up to all 128) discriminators. This feature and the test mode as a whole were added as a back-up diagnostic tool that allows to investigate the front-end even if the back-end was faulty, or likewise to investigate the back-end if the front-end was inoperative. With test pulses enabled (bit 0 of control register 32 set to

- Additionally, with test pulses disabled, this test trigger mode may be employed to realize an analogue base-level measurement for every channel,

1), test pulses may be injected into the front-end also in test trigger mode.

Figure 12: Generation of test signals.

as upon a trigger signal on TestPulse, all non-masked channels are forced into taking an analogue sample of the signal with the respective peak detector, which may then be read out.

Note: When test\_pulse is disabled, all the switches at the inputs of the frontend channels are opened (compare with figure 13). The test pulse generator is not only inactive but rather entirely disconnected.

The generation of the test signals is depicted in figure 12. Both signals originate from the external TestPulse pad (pad 217) and are enabled by appropriate configuration bits, as shown in the figure. The signals can be synchronized on the rising edge of the clk256A, and delayed by setting the I2C registers 38 and 39. The test\_pulse signal polarity can also be controlled by a configuration bit.

#### 4.7 Internal Test Pulses

An internally generated test pulse may be coupled into every channel of the ASIC when test pulse enable is selected (configuration register 32, bit 0 set to 1). The amount of charge injected is controlled through register cal (reg. 24). One of four test pulse generators is activated and sends test pulses to the channels belonging to one of four groups of 32 channels, selectable through configuration register 33, bits 0 and 1 (see table 8). For the test pulse to be injected into any channel, the channel additionally needs to be connected to its respective coupling capacitor. This is done by means of the mask register. A mask bit 1 disconnects the channel (see figure 13).

The last requisit for a test pulse to be injected is a positive edge on the single ended digital input "TestPulse" (input pad 217). The test pulse may be issued synchronized to the clock (configuration register 32 bit 1 set to one) or entirely asynchronous. Further, when synchronous, it may be issued delayed with respect to the clock (delay register 38 bits 0–7). Its polarity is determined through configuration register 32 bit 2 (0 corresponds to positive charge, 1 to negative charge). The control scheme of the test pulse generation is depicted in figure 12.

**Note:** The test channel cannot be masked and belongs to the group of channels selected by configuration register 33 bits 0–1 being set to 11.

In response to a full swing square wave at the strobe input TestPulse, the

Figure 13: Block diagram of the connection between calibration circuit and channel inputs. The signals sel(127:0) are controlled through the mask registers (I<sup>2</sup>C reg. 0 - 15), EnableB(3:0) correspond to configuration register 33 (bits 0 and 1) and the digital signal strobe corresponds to the externally applied signal TestPulse (pad 217) 30

calibration circuit generates voltage steps across the capacitor coupling into the channel input. The test capacitor of C=100 fF is stimulated with a voltage step that injects the charge  $Q=C\cdot \Delta V$ . The step height may be programmed through I<sup>2</sup>C register 24 cal from 0 to 1.137 V.

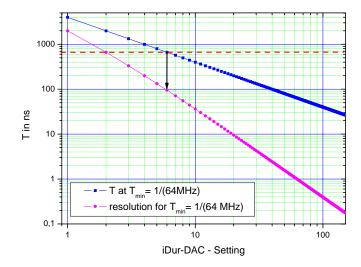

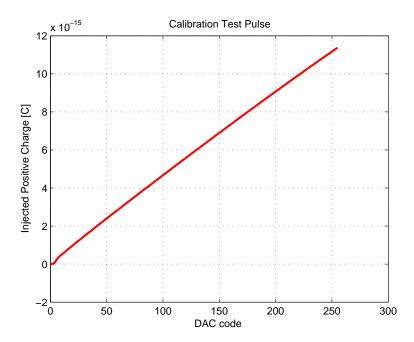

Figure 14: Injected positive charge during the calibration procedure.

The corresponding injected charge at the input of the preamplifier is variable in 256 steps from 0 fC to 11.37 fC. The amount of charge injected as a function of cal-register setting as simulated is displayed in figure 14 for positive charge and figure 15 negative charge.

The least mean square approximation with a linear function of the calibration curve yields a DAC gain of 44.63 aC/LSB for the positive charge and -44.55 aC/LSB for the negative charge with 0 C offset for positive charge and 0 C offset for the negative charge.

Least mean square linear function fitting curve:

$$\texttt{positive test charge}[C] = \frac{44.52 \ aC}{LSB} \cdot Reg24Value[LSB] + 162.7 \ aC$$

$$\texttt{negative test charge}[C] = \frac{-44.41 \; aC}{LSB} \cdot Reg24Value[LSB] - 182.0 \; aC$$

where Reg24Value[LSB] is the value written into the cal register (I<sup>2</sup>C register 24).

Figure 15: Injected negative charge during the calibration procedure.

# 4.8 Comparator Operation and Time Walk Compensation

The comparator circuit consists of an integrator, a threshold generator and a discriminator. The integrator tracks the DC-offset of the shaped pulse with a variable time constant

To correlate the signals on the x- and y-plane of a detector by means of a time stamp, a discriminator has to detect these signals without any dependency on the signal amplitude. A single pulse discriminator is followed by a voltage controlled delay circuit, which is used to compensate the time walk. With this circuit a reduction of the comparator's time dependency to less than 2 ns has been achieved.

The output of the *time walk* compensation circuit is not only used to latch a 14 bit time-stamp, but also to arm the peak detector and hold circuit connected to the slow channel.

The DC-offsets vary from channel to channel. It is added to the threshold voltage. The threshold level is adjustable with a resolution of 5 bits per channel.

# 4.9 Clock Signals

The n-XYTER is fed with a clock signal of nominally 256 MHz. It is used to run the internal digital circuitry as well as to generate data transmission clocks 128 MHz and 32 MHz. Finally, clock clk256 is used to generate a time-stamp of 1 ns resolution and to synchronize test pulses.

The chip has two clock inputs (LVDS):

- clk256A is the main clock. It is employed for time stamp generation, sychronization of internally generated test signals (test\_pulse and test\_trigger) and for readout clock generation.

- *clk256B* is the secondary clock. It is used for an alternative readout clock generation as well as an alternative time-stamp LSB generation.

The configuration is set through the configuration registers 32 and 33. Functions:

- time stamp LSB generation It may be selected, whether clk256A or clk256B should be used to derive the LSB of the time stamp. This is done by setting the TSB LSB clock select bit (Configuration register 32, bit 7) to 0 (derive LSB from clk256A on chip) or logic 1 (derive LSB from clk256B). The latter option was provided as an alternative, should one encounter any difficulties in shifting clk256A on chip. A 90° phase shifted clock signal clk256B needs to be applied externally in this case (c.f. 16).

- synchronization of the test signals (test pulse, test trigger)

- readout clock generation (see next section for details)

# 4.9.1 Time Stamp Generation

Upon registry of a signal, a time-stamp is issued and registered to be stored in the respective channel FIFO together with the analogue signal peak height. This time-stamp is generated by means of a gray-encoded counter, the state of which is latched upon a trigger as the momentary time-stamp.

The homogeneous 14-bit time-stamp is built up from a 12-bit gray-encoded counter (bits 13:2), a toggle flip-flop (bit 1) and the buffered input clock (bit 0). With the adequate phase relation between bits 0, 1 and 2, a homogeneous 14-bit time-stamp counter is set-up.

The mechanism of time-stamp generation provides some alternatives that may be programmed. The simplified block schematic depicting the time stamp generation circuit is presented in figure 16.

The right timing between bits 1 and 2 is achieved by setting  $I^2C$  register 43 to appropriate values. A phase shift by -90° should be achieved on bit 1. The timing between bit 0 and 1 may be controlled through registers 44 and 45. Here, also, the signal needs to be shifted by -90° with respect to itself.

The clocks for chip operation can be generated in two ways, described in table 11: The clk256A LVDS input may be used in combination with clk256B according to the value of TS LSB clock select (bit 7 of Configuration Register 32). When TS LSB clock select (bit 7 of the Configuration Register 32) is low (0) the LSB of the time stamp is derived from clk256A, if it is high (1) the LSB of the time stamp is derived from clk256B.

If the n-XYTER is to be operated with just one input clock, clk256A, bit 7 of Configuration Register 32 should be set to 0 so that the LSB of the time-stamp

Figure 16: Time-stamp generation principle

will be internally generated (see chapter 4.9). For homogeneous time bining, registers 43 to 45 then need to be adjusted. This should be the normal clock operation mode.

The other, optional mode, was included as a fall back solution in case any circuitry should have resulted faulty. To operate the n-XYTER with two, phase shifted input clocks, clk256A and clk256B, Configuration Register 32, bit 7 needs to be set to 1. In this case, only delay register 43 is relevant. The externally imposed phase shift between clk256A and clk256B further determines homogeneity of the time stamp.

TS LSB clock select (bit 7 of Configuration Register 32):

- when 0, the LSB of the time stamp is derived from clk256A

- when 1, the LSB of the time stamp is derived from clk256B

The internal structure of the delay buffers is presented in figure 11. The effective delay of the buffer may be programmed by attaching capacitive loads to the outputs of four serially connected inverters. Note that pairs of capacitors are connected serially to optimize minimum delay of the buffer.

The presented configuration allows adjusting of the delays for input clk256A clock frequencies from 128 MHz to 256 MHz.

#### 4.9.2 Readout clocks

The n-XYTER uses internally generated readout clocks which are accessible from two pairs of LVDS output pins:

- 32 MHz is used in the token ring, the memories and the analogue multiplexer. It is available on an LVDS output.

- 128 MHz is used for data transfer off the chip and is likewise available on an LVDS output.

By default, after reset of the I<sup>2</sup>C registers, readout clock and data transmission clock are derived directly from *clk256B*. For operation in this setting, *clk256B* should be driven at 128 MHz in order to obtain the normal data transfer frequency. The start-up default is the one operating at lower frequency. For operation at the nominal frequency of 256 MHz, the clock configuration needs to be modified by setting bit 3 of Configuration Register 33 to 1. This is the normal operation mode!

Readout clock select (bit 3 of Configuration Register 33)

- when 0 (startup setting), the readout clock is obtained by dividing *clk256B* by 4, the data transmission clock *clk128* is the buffered clock *clk256B*.

- when 1 (normal operation mode), the readout clock at 32 MHz and the clock for the digital output buffer (also called transmission clock) at 128 MHz, are obtained by dividing *clk256A* by 8 and by 2 respectively.

## 5 Data Transfer

Data read out from the local FIFOs through the token ring is then synchronously transferred off the chip. To this end, the analogue data is fed into a dedicated differential readout buffer at the token ring operating rate of 32 MHz, while the digital data gets multiplexed fourfold onto 8 differential LVDS output lines. In this scheme, every data element consists of a 14 bit time-stamp, a six bit channel number and three additional diagnostic bits. The analogue differential output buffer is designed for a differential output impedance of 100 Ohms.

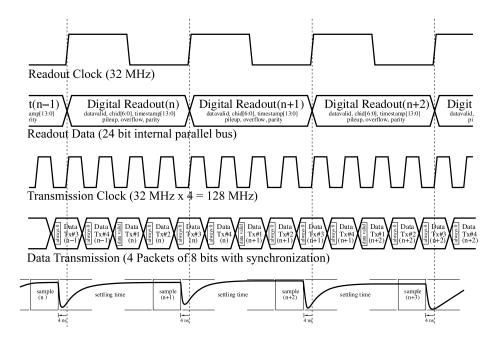

# 5.1 Digital Output Format and Timing

For each recorded pulse a total of 25 significant bits will be sent off chip.

Data bits are split into 4 8-bit packets, transmitted at 4 times the main clock frequency (i.e.  $4 \times 31.25 \text{ MHz} = 125 \text{ MHz}$ ).

The token is generated when at least one FIFO has data in it (the FIFO has a *empty* signal which trigger the token generation), the token comes out from the token manager circuit and starts to travel in the ring. Once the token arrives at the channel which contains data, it stops and generate a signal *read* to get the data out from the FIFO memory. Then, at the next read out clock cycle, it goes on and stops to the next channel which contains data. If there are

no more channels which have data, the token reaches the token manager. When the token manager recognize the condition to restart this procedure (at least one FIFO has data in it) it releases the token again and repeats all the above steps.

When the FIFOs are read, both the analog (pulse amplitude) and digital information (timestamp, channel id, data valid, pile up signal, overflow signal) are sent to the output.

If no data is avaliable from the FIFOs, the Data Valid bit (bit 7 in the first packet) is always 0.

Output is differential LVDS standard.

In some circumstances, the data valid (DV) bit (the bit 7 of the first packet) is not properly set, even if the timestamp is valid and the interal circuits recognize and record the event. The data might reach the output with the the data valid (DV) bit (the bit 7 of the first packet) stucked at 0, all the remaining bits of the 4 packets are indeed valid.

7 6 5 3 2 0 0  $\overline{\mathrm{DV}^{\ 1}}$  $\overline{\text{TS13}}$  $\overline{\text{TS}12}$  $\overline{\text{TS}11}$  $\overline{\text{TS}10}$  $\overline{\mathbf{TS9}}$  $\overline{\mathbf{TS8}}$  $\overline{\mathbf{TS7}}$ TS6TS5TS4 TS3TS2TS1 TS00 1 2 0 ID6ID5ID4ID3ID2ID1 ID03 0 0 0 0 0 PileUp OverF Parity

Table 12: Digital Output Format

Table 13: Digital Output Format when no data is avaliable from the channels

|   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 2 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 3 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

Data packets are transferred at the readout clock frequency of nominally 32 MHz. The sequence of four bytes is however not in phase with clk32MHz but rather shifted by 180°.

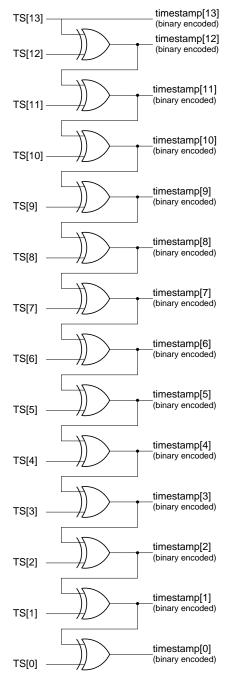

The output packets contain Gray encoded data. To convert from the Gray code format to binary code format the table 18 in Appendix E provides the translation for the time-stamp and table 19 in Appendix E provides the translations for the channel identifier. The circuits in the FPGA might use the suggested circuit shown in figure 18 to decode the time-stamp information and the circuit shown in figure 19 to decode channel ID information.

#### 5.2 Analogue Data Transfer, Timing

For every data element identified by the token ring for data readout, the corresponding local analogue FIFO pulse hight storage cell is connected to the analogue readout bus and fed to the analogue readout buffer. As the token ring

<sup>&</sup>lt;sup>1</sup>data valid

### Analogue Output

Figure 17: Output data diagram for timing reference. Note that the analogue output data is valid about 4 ns prior to the 32 MHz frame clock. Also, transmitted data is not in phase with the readout clock clk32MHz also transmitted.

initiates readout at the frequency of clk32MHz, analogue data values are generated at the analogue output buffer at this frequency too as long as there is valid data stored in channel FIFOs. The analogue data chain is designed to cope with this data rate. Nevertheless, the maximum available time should be employed for the signal to settle before readout.

Figure 17 shows the sequence of data as it is transferred off the chip. Note in particular, that corresponding data elements are time shifted. Further more, the analogue signal is to be sampled as late as possible within the data frame as settling of the signal needs to be accounted for. Measurements show that a repeated transfer is initiated yet even before the data frame clock (32 MHz) transits in its positive edge.

The analogue signal is valid 4ns prior to the 32MHz positive clock transition. It should be sampled as late as possible

The sampling point of for the analogue data appears about  $\frac{5}{4}$  of a read-

out frame earlier than the first data element of the digital packet. In practical considerations, the existence of this delay is irrelevant, as any external ADC connected to the analogue data line will introduce its own additional delays, so that energy and timing information will need to be aligned in any case after signal conversion.